At the 2024 TSMC OIP Ecosystem Forum, one of the technical talks by TSMC focused on maximizing 3DIC design productivity and rightfully so. With rapid advancements in semiconductor technology, 3DICs have become the next frontier in improving chip performance, energy efficiency, and density. TSMC’s focus on streamlining the design process for these cutting-edge solutions has been critical, and 3DBlox is central to this mission. 3DBlox is an innovative framework inclusive of a standardized design language, introduced by TSMC aimed at addressing the complexities of 3D integrated circuit (3DIC) design. The following is a synthesis of that talk, delivered by Jim Chang, Deputy Director at TSMC for the 3DIC Methodology Group.

Progress from 2022 to 2023: Laying the Foundations for 3DBlox

In 2022, TSMC began exploring how to represent their 3DFabric offerings, particularly CoWoS (Chip-on-Wafer-on-Substrate) and INFO (Integrated Fan-Out), which are critical technologies for 3DIC. CoWoS integrates chips using a silicon interposer, while INFO uses RDL (Redistribution Layer) interposers. TSMC combined these approaches to create CoWoS-R, replacing the silicon interposer with RDL technology, and CoWoS-L, which integrates local silicon interconnects.

With these building blocks in place, TSMC realized that they needed a systematic way to represent their increasingly complex technology offerings. This led to the creation of 3DBlox, which provided a standard structure for representing all possible configurations of TSMC’s 3DFabric technologies. By focusing on three key elements—chiplets, chiplet interfaces, and the connections among interfaces—TSMC was able to efficiently model a wide range of 3DIC configurations.

By 2023, TSMC had honed in on chiplet reuse and design feasibility, introducing a top-down methodology for early design exploration. This methodology allowed TSMC and its customers to conduct early electrical and thermal analysis, even before having all the design details. Through a system that allowed for chiplets to be mirrored, rotated, or flipped while maintaining a master list of chiplet information, TSMC developed a streamlined approach for design rule checking across multiple chiplets.

Innovations in 2024: Conquering Complexity with 3DBlox

By 2024, TSMC faced the growing complexity of 3DIC systems and devised new strategies to address it. The key innovation was breaking down the 3D design challenge into more manageable 2D problems, focusing on the Bus, TSVs (Through-Silicon Vias), and PG (Power/Ground) structures. These elements, once positioned during the 3D floorplanning stage, were transformed into two-dimensional issues, leveraging established 2D design solutions to simplify the overall process.

Key Technology Developments in 2024

TSMC’s focus on maximizing 3DIC design productivity in 2024 revolved around five major areas of development: design planning, implementation, analysis, physical verification, and substrate routing.

Design Planning: Managing Electrical and Physical Constraints

In 3DIC systems, placing the Bus, TSVs, and PG structures requires careful attention to both electrical and physical constraints, especially Electromigration and IR (EMIR) constraints. Power delivery across dies must be precise, with the PG structure sustaining the necessary power while conserving physical resources for other design elements.

One of TSMC’s key innovations was converting individual TSV entities into density values, allowing them to be modeled numerically. By using AI-driven engines like Cadence Cerebrus Intelligent Chip Explorer and Synopsys DSO.ai, TSMC was able to explore the solution space and backward-map the best solutions for bus, TSV, and PG structures. This method allowed designers to choose the best tradeoffs for their specific designs.

Additionally, chip-package co-design was emphasized in 2024. TSMC collaborated with key customers to address the challenges of coordinating between the chip and package teams, which previously operated independently. By utilizing 3DBlox’s common object format and common constraints, teams could collaborate more efficiently, settling design constraints earlier in the process, even before Tech files were available.

Implementation: Enhancing Reuse and Hierarchical Design

As customers pushed for increased chiplet reuse, TSMC developed hierarchical solutions within the 3DBlox language to support growing 3DIC designs. With the increasing number of alignment marks required to align multiple chiplets, TSMC worked closely with EDA partners to identify the four primary types of alignment markers and automate their insertion in the place-and-route flow.

Analysis: Addressing Multi-Physics Interactions

![]()

Multi-physics interactions, particularly related to thermal issues, have become more prominent in 3DIC design. TSMC recognized that thermal issues are more pronounced in 3DIC than in traditional 2D designs due to stronger coupling effects between different physical engines. To address this, TSMC developed a common database that allows different engines to interact and converge based on pre-defined criteria, enabling efficient exploration of the design space.

![]()

One of the critical analysis tools introduced in 2024 was warpage analysis, crucial as the size of 3DIC fabric grows. TSMC developed the Mech Tech file, defining the necessary information for industry partners to facilitate stress simulation, addressing a gap in warpage solutions within the semiconductor industry.

Physical Verification: Ensuring Integrity in 3DIC Designs

TSMC tackled the antenna effect, a manufacturing issue where metal may accumulate plasma charges that can penetrate gate oxides via TSVs and bumps. By collaborating with EDA partners, TSMC created a design rule checking (DRC) deck that models and captures the antenna effect, ensuring it can be accounted for during the design process.

In 2024, TSMC also introduced enhancements in layout vs. schematic (LVS) verification for 3DIC systems. Previously, LVS decks assumed a one-top-die, one-bottom-die configuration. However, 3DBlox’s new automated generation tools allow for any configuration to be accurately verified, supporting more complex multi-die designs.

Substrate Routing: Tackling the Growing Complexity

As 3DIC integration grows in scale, so does the complexity of substrate routing. Substrate design has traditionally been a manual process. The growing size of substrates, combined with the intricate requirements of modern 3DIC designs, necessitated new innovations in this space.

TSMC’s work on Interposer Substrate Tech file formats began three years ago, and by 2024, they were able to model highly complex structures, such as the inclusion of tear drops in the model. This advancement offers a more accurate and detailed representation of substrates, crucial for the larger and more intricate designs emerging in the 3DIC space. TSMC worked with their OSAT partners through the 3DFabric Alliance to support this format.

Summary: 3DBlox – Paving the Way for 3DIC Innovation

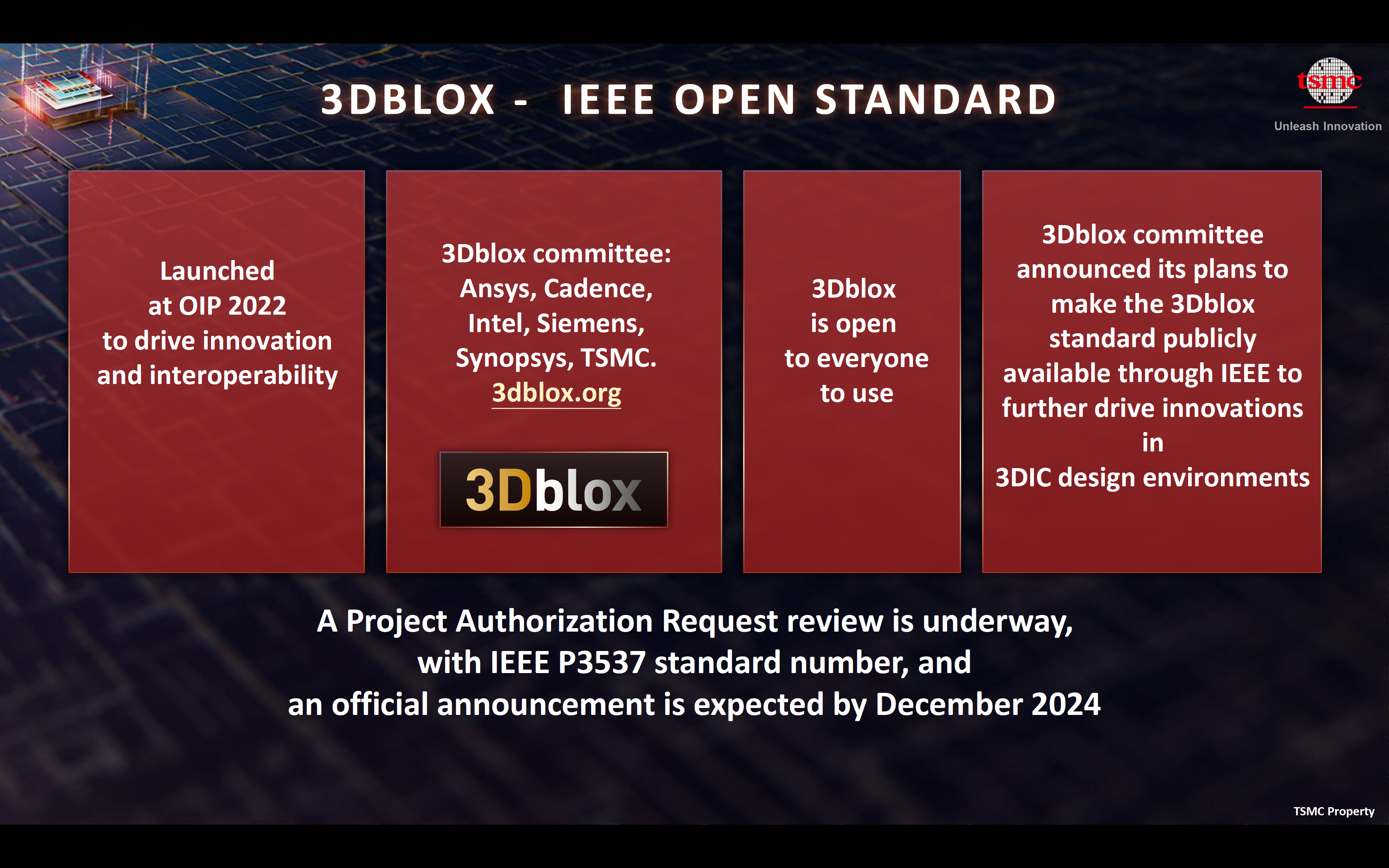

TSMC’s 3DBlox framework has proven to be a crucial step in managing the complexity and scale of 3DIC design. From early exploration and design feasibility in 2023 to breakthroughs in 2024 across design planning, implementation, analysis, physical verification, and substrate routing, TSMC’s innovations are paving the way for more efficient and scalable 3DIC solutions. As the industry moves toward even more advanced 3D integration, the 3DBlox committee announced plans to make the 3DBlox standard publicly available through IEEE. 3DBlox will continue to play a vital role in enabling designers to meet the increasing demands of semiconductor technology for years to come.

Also Read:

Synopsys and TSMC Pave the Path for Trillion-Transistor AI and Multi-Die Chip Design

TSMC 16th OIP Ecosystem Forum First Thoughts

TSMC OIP Ecosystem Forum Preview 2024

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.