2.5D and 3D multi-die design is rapidly moving into the mainstream for many applications. HPC, GPU, mobile, and AI/ML are application areas that have seen real benefits. The concept of “mix/match” for chips and chiplets to form a complex system sounds deceptively simple. In fact, the implementation and analysis techniques required… Read More

Tag: ir drop

Maximizing 3DIC Design Productivity with 3DBlox: A Look at TSMC’s Progress and Innovations in 2024

At the 2024 TSMC OIP Ecosystem Forum, one of the technical talks by TSMC focused on maximizing 3DIC design productivity and rightfully so. With rapid advancements in semiconductor technology, 3DICs have become the next frontier in improving chip performance, energy efficiency, and density. TSMC’s focus on streamlining the… Read More

Calibre DesignEnhancer Improves Power Management Faster and Earlier

Anyone who has attempted to implement a custom design in an advanced process node knows that effective power management can be quite challenging. Effects such as voltage (IR) drop and electromigration (EM) can present significant headaches for both design teams and foundries. Optimizing layouts for these kinds of issues is … Read More

Agile Analog Visit at #60DAC

Chris Morrison, Director of Product Marketing at Agile Analog met with me on the Tuesday at DAC this year, and I asked what has changed in the last year for their analog IP business. The short answer is that the company has initially built up foundation IP for Analog Mixed-Signal (AMS) uses, then recently added new IP for data conversion,… Read More

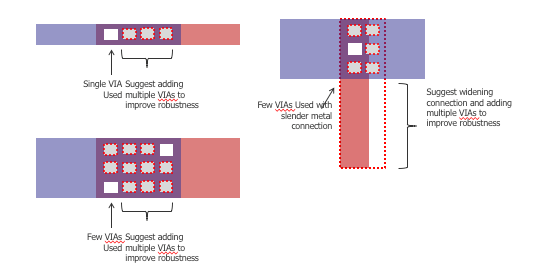

Calibre’s next move – Correct-by-Construction IC Layout Optimization

Siemens EDA’s next move in its Calibre shift left strategy is the addition of correct-by-construction IC layout optimization for the most critical emerging physical design challenges. Calibre’s new DesignEnhancer product supports both custom and digital ICs and is already in use by several leading IC design companies. It … Read More

Electromigration and IR Drop Analysis has a New Entrant

My first IR drop analysis was back in the early 1980s at Intel, where I had to manually model the parasitics of the VDD and VSS interconnect for all of the IO cells that our team was designing in a graphics chip, then I ran that netlist in a SPICE simulator using transient analysis, measuring the bounce in VSS and droop in VDD levels as all… Read More

Reliability Analysis for Mission-Critical IC design

Mission-critical IC design for segments like automotive, aerospace, defense, medical and 5G have more stringent reliability analysis requirements than consumer electronics, and entails running special simulations for the following concerns:

- Electromigration analysis

- IR drop analysis

- MOS aging

- High-sigma Monte Carlo

Webinar: Multicycle Vectorless Dynamic IR Signoff for Near 100 Percent Coverage

Check this webinar out – Mediatek will share a novel approach to early IR drop estimation. Competition in system design has become even more intense because potential markets are huge and there are more players with deep pockets chasing those markets. Wherever you are in those value chains, you want to shift everything left to accelerate… Read More

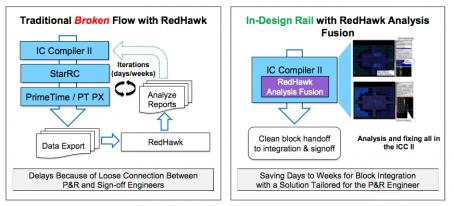

Integrity, Reliability Shift Left with ICC

There is a nice serendipity in discovering that two companies I cover are working together. Good for them naturally but makes my job easier because I already have a good idea about the benefits of the partnership. Synopsys and ANSYS announced a collaboration at DAC 2017 for accelerating design optimization for HPS, mobile and automotive.… Read More

Foundry Partnership Simplifies Design for Reliability

This builds on a couple of topics I have covered for quite a while from an analysis point of view – integrity and reliability. The power distribution network and some other networks like clock trees are particularly susceptible to both IR-drop and electromigration (EM) problems. The first can lead to intermittent timing failures,… Read More