You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

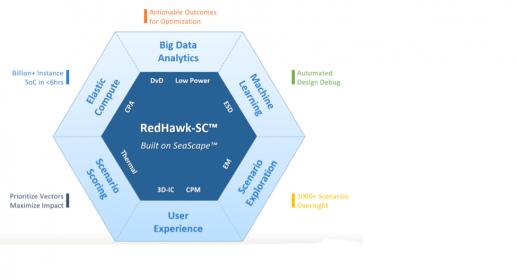

While it’s interesting to hear a tool-vendor’s point of view on the capabilities of their product, it’s always more compelling to hear a customer/user point of view, especially when that customer is NVIDIA, a company known for making monster chips.

A quick recap on the concept. At 7nm, operating voltages are getting much closer… Read More

Silvaco Swallows Invarianby admin on 03-20-2015 at 7:00 amCategories: EDA

Yesterday, Silvaco announced that it has acquired Invarian Inc. Details of the transaction were not disclosed.

Who is Invarian? They are a recognized leader in block-level to full-chip sign-off analysis for complex, high-performance ICs. Their unique methodology utilizes a parallel architecture and concurrent power-voltage-thermal… Read More

One of the big challenges in designing ICs today is designing a robust power net capable of delivering necessary current levels to all areas of the die. Getting it wrong can, of course, lead to circuit failures that range from non-functional silicon, through intermittent performance and functional problems, to early EM-driven… Read More

One of the big challenges in a modern SoC is doing an accurate analysis of the power nets. Different layers of metal have very different resistance characteristics (since they vary so much in width and height). Even vias can cause problems due to high resistance. Typically power is distributed globally on high-level metal layers,… Read More

You probably remember Cadence introduced Voltus towards the end of last year at their signoff summit. This was aimed at digital designers. Prior to that they had announced Tempus, their static timing analysis tool. More recently they announced Quantus QRC extraction. All of these tools that end in -us have been re-architected… Read More

In this age of SoCs with hundreds of IPs from different sources integrated together and working at high operating frequencies, FPGA designers are hard pressed keeping up the chip reliability from issues arising out of excessive static & dynamic IR drop, power & ground noise, electro migration and so on. While the IPs are… Read More

Often it is considered safer to be pessimistic in estimating IR-drop to maintain power integrity of semiconductor designs; however that leads to the use of extra buffering and routing resources which may not be necessary. In modern high speed, high density SoCs having multiple blocks, memories, analog IPs with different functionalities… Read More

Ground. It’s that little downward-pointing triangle that somehow works miracles on every schematic. It looks very simple until one has to tackle modern power distribution network (PDN) design on a board with high speed and high power draw components, and you soon discover ground is a complicated fairy tale with a lot of influences.… Read More

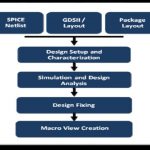

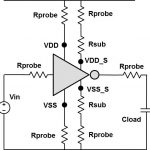

Designing custom IP blocks is a challenge at the transistor-level and I wanted to learn what the recommended methodology and EDA tool flow was at Synopsys. They have a webinar that you can register for and it takes 30 minutes to learn what they have to say, or you can read a White Paper. If you cannot spare that much time, then my summary… Read More