2.5D and 3D multi-die design is rapidly moving into the mainstream for many applications. HPC, GPU, mobile, and AI/ML are application areas that have seen real benefits. The concept of “mix/match” for chips and chiplets to form a complex system sounds deceptively simple. In fact, the implementation and analysis techniques required… Read More

Tag: electromigration

Addressing Reliability and Safety of Power Modules for Electric Vehicles

As electric vehicles (EVs) gain widespread adoption, safety, reliability, and efficiency are becoming increasingly important. A crucial component in ensuring these aspects is the power module (PM), which manages the energy flow between the EV battery and the motor. The design of these power modules must not only meet the high-performance… Read More

Maximizing 3DIC Design Productivity with 3DBlox: A Look at TSMC’s Progress and Innovations in 2024

At the 2024 TSMC OIP Ecosystem Forum, one of the technical talks by TSMC focused on maximizing 3DIC design productivity and rightfully so. With rapid advancements in semiconductor technology, 3DICs have become the next frontier in improving chip performance, energy efficiency, and density. TSMC’s focus on streamlining the… Read More

Calibre DesignEnhancer Improves Power Management Faster and Earlier

Anyone who has attempted to implement a custom design in an advanced process node knows that effective power management can be quite challenging. Effects such as voltage (IR) drop and electromigration (EM) can present significant headaches for both design teams and foundries. Optimizing layouts for these kinds of issues is … Read More

Electromigration and IR Drop Analysis has a New Entrant

My first IR drop analysis was back in the early 1980s at Intel, where I had to manually model the parasitics of the VDD and VSS interconnect for all of the IO cells that our team was designing in a graphics chip, then I ran that netlist in a SPICE simulator using transient analysis, measuring the bounce in VSS and droop in VDD levels as all… Read More

Reliability Analysis for Mission-Critical IC design

Mission-critical IC design for segments like automotive, aerospace, defense, medical and 5G have more stringent reliability analysis requirements than consumer electronics, and entails running special simulations for the following concerns:

- Electromigration analysis

- IR drop analysis

- MOS aging

- High-sigma Monte Carlo

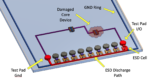

Magwel Adds Core Device Checking for ESD Verification

In the past ESD sign-off has been accomplished by a combination of techniques. Often ESD experts are asked to look at a design and assess its ESD robustness based on experience gained from prior chips. Alternatively, designers are told to work with a set of rules given to them, again based on previous experience about what usually… Read More

VLSI Symposium 2020 – Imec Buried Power Rail

The 2020 VLSI Technology Symposium was held as a virtual conference from June 14th through June 19th. At the symposium Imec gave an interesting paper on Buried Power Rails (BPR) and I had a chance to interview one of the authors, Anshul Gupta.

As logic devices continue to scale down metal pitch is reaching a limit. Imec defines a pitch… Read More

Free Webinar on Verifying On-Chip ESD Protection

Walking across a carpet can generate up to 35,000 volts of static charge, which is tens of thousands of times higher than the operating voltages of most integrated circuits. When charge build up from static electricity is exposed to the pins of an IC, the electrostatic discharge (ESD) protection network on the chip is intended to… Read More

ANSYS, TSMC Document Thermal Reliability Guidelines

Advanced IC technologies, 5nm and 7nm FinFET design and stacked packaging, are enabling massive levels of integration of super-fast circuits. These in turn enable much of the exciting new technology we hear so much about: mobile gaming and ultra-high definition mobile video through enhanced mobile broadband in 5G, which requires… Read More