The symbol for a PowerMOS device in a converter circuit schematic looks simple enough. However, it belies a great deal of hidden complexity. A single device is actually a huge array of parallel intrinsic devices connected together to act as a single high power device. While their gate lengths are small, as with many other MOS devices,… Read More

Tag: electromigration

Foundry Partnership Simplifies Design for Reliability

This builds on a couple of topics I have covered for quite a while from an analysis point of view – integrity and reliability. The power distribution network and some other networks like clock trees are particularly susceptible to both IR-drop and electromigration (EM) problems. The first can lead to intermittent timing failures,… Read More

Webinar: Thermal and Reliability for ADAS and Autonomy

OK, so maybe the picture here is a little over the top, but thermal and reliability considerations in automotive in general and in ADAS and autonomy in particular, are no joke. Overheating, thermal-induced EM and warping at the board-level, in the package or interposers, are concerns in any environment but especially when you’re… Read More

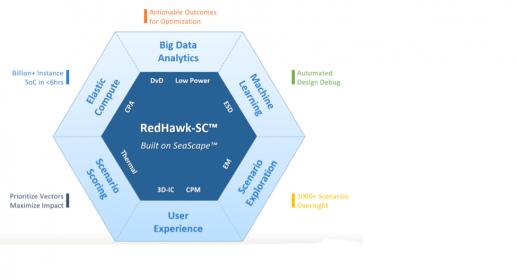

Big Data Analytics and Power Signoff at NVIDIA

While it’s interesting to hear a tool-vendor’s point of view on the capabilities of their product, it’s always more compelling to hear a customer/user point of view, especially when that customer is NVIDIA, a company known for making monster chips.

A quick recap on the concept. At 7nm, operating voltages are getting much closer… Read More

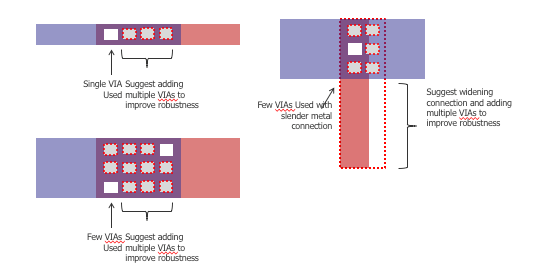

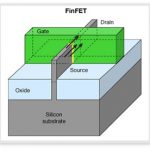

Reliability Signoff for FinFET Designs

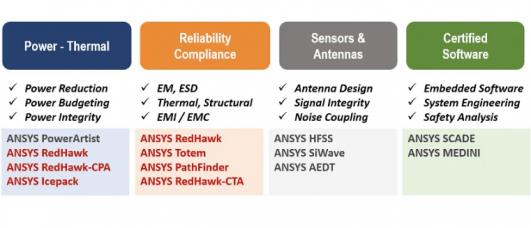

Ansys recently hosted a webinar on reliability signoff for FinFET-based designs, spanning thermal, EM, ESD, EMC and aging effects. I doubt you’re going to easily find a more comprehensive coverage of reliability impact and analysis solutions. If you care about reliability in FinFET designs, you might want to check out this webinar.… Read More

Webinar: Signoff for Thermal, Reliability and More in Advanced FinFET designs

In automotive applications, advanced FinFET processes are great for high levels of integration and low power. But they also present some new challenges in reliability signoff. Ansys will be hosting a webinar to highlight the challenges faced by engineers trying to ensure thermal, electromigration (EM) and electrostatic discharge… Read More

Simulating ADAS

Simulation is a broad technique spanning certainly digital logic and circuit simulation but also methods beyond these which are particularly relevant to ADAS design. In fact, much of the design of full ADAS systems begins and ends with these types of modeling. This is in part due to the need fully validate integrity and reliability… Read More

Integrity and Reliability in Analog and Mixed-Signal

In the largest and fastest growing categories in electronics – mobile, IoT and automotive – analog is playing an increasingly important role. It’s important in delivering high integrity power and critical signals to the design though LDO regulators and PLLs, in managing high speed interfaces like DDR and SERDES, in interfacing… Read More

Top Ten #53DAC Highlights

Here is a very subjective list of the Top 10 logistical and technical highlights from DAC’53.

(10) With DAC attendance down from its peak days, the Austin Convention Center served as an excellent venue. There was good participation from companies with design centers in the “Silicon Hills”. And, I saw colleagues from Silicon Valley,… Read More

The Importance of Transistor-Level Verification

According to the IEEE Std 1012-2012, verification is the acknowledgement that a product is in satisfactory condition by meeting a set of rigorous criteria. [3] Transistor-level verification involves the use of custom libraries and design models to achieve ultimate performance, low power, or layout density. [2] Prediction… Read More