The start of the new year is typically a time for annual predictions. Prognostications are especially difficult in our industry, due to the increasing difficulty in Moore’s Law technology scaling and greater design complexity challenges. There is one sure prediction, however — this year will see the emergence of embedded FPGA (eFPGA) IP integration into a diverse set of SoC products.

I recently had the opportunity to chat with Geoff Tate, CEO of Flex Logix Technologies, Inc., a start-up IP development company, whose innovative eFPGA IP is helping lead this adoption. Geoff educated me on the markets where eFPGA IP is being integrated, as well as the unique characteristics and customer requirements for eFPGA design enablement.

The market opportunities for eFPGA integration are vast. A data encryption accelerator IP core may utilize different (and evolving) security algorithms, depending upon the target application. Digital signal processing (DSP) algorithms can be implemented in programmable eFPGA hardware, executing more efficiently than utilizing software running on a core processor. Data bus communication protocols, both on-chip and off-chip, are also varied and evolving — the availability of a programmable controller would accelerate the release availability of a new SoC design.

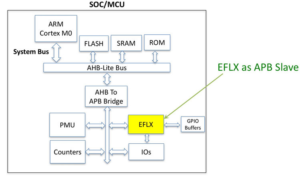

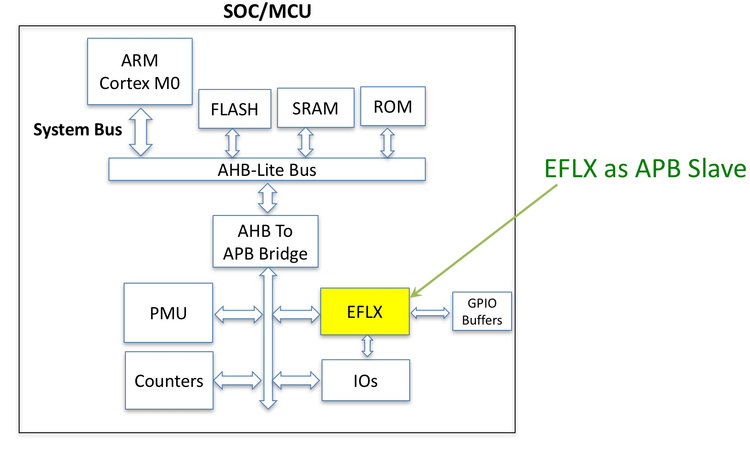

Flex Logix EFLX eFPGA IP as an Advanced Peripheral Bus controller

And, perhaps most importantly, an eFPGA core enables a single SoC part number to reach multiple markets, saving development, qualification, and production costs over a comparable SoC implementation.

In many respects, embedded FPGA IP is similar to the standalone, commercial FPGA module. The logic functionality is reconfigurable — parts can be updated at production test, at system test, or in the field. The eFPGA implementation flow utilizes an RTL synthesis algorithm optimized for mapping to the programmable logic capabilities of individual Look-Up Table (LUT) cells — the Flex Logix flow incorporates the familiar Synopsys Synplify synthesis tool. Subsequent placement and routing algorithms define how the existing switch and interconnect segment resources will be assigned. The EFLX compiler is provided for physical implementation and bit file configuration. The compiler provides delay models for subsequent static timing analysis.

Commercial FPGA technology is well-established. Given the market potential described above, why hasn’t eFPGA IP been more readily integrated by now? Why will 2017 finally be the year of the eFPGA?

Geoff shared some insights into the challenges of developing eFPGA technology, and the unique approaches that Flex Logix has pursued. “The customer requirements for reconfigurable functionality are extremely diverse, from high-performance networking to low-power, cost-sensitive applications. Flex Logix has silicon testsite data in process technologies ranging from 40nm (e.g., TSMC’s 40LP/ULP)to 16nm(e.g., TSMC’s 16FF+ and 16FFC). The low-power customers have access to the full sleep-mode power domain implementation available in the eFPGA IP core.”

In addition to the breadth of technology support, Geoff impressed upon me the key characteristics of the Flex Logix eFPGA strategy. The LUT logic resources available in each eFPGA are available in two variants:

- a more conventional programmable function (e.g., 2 X 4-input logic input functions plus two available flop inputs in each LUT, expanding to more logic inputs in newer process technologies)

- a unique “DSP-centric” LUT, with functionality that accelerates multiply/add/accumulate (MAC) computation

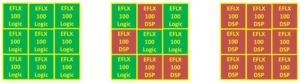

These different LUT types can be readily intermixed, when implementing the embedded IP core.

EFLX logic and DSP LUT building blocks can be freely intermixed

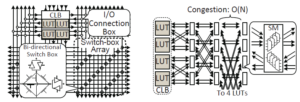

In addition to the variability in LUT cells, Flex Logix has implemented a unique “hierarchical” switch network.

Illustration of FPGA conventional and hierarchical switch array. Source: Wang, et al., “A 1.1 GOPS/mW FPGA Chip with Hierarchical Interconnect Fabric”, VLSI Technology Symposium 2011.

Commercial FPGA parts utilize large switch transistor crossbar arrays to connect to interconnect resources — for example, 80% of the transistors used on an FPGA are often utilized for interconnect. Conversely, Flex Logix has pursued a more modular architecture, where small groups of LUT’s share a local switch matrix and local route segments, with additional stages of switches utilized for global routes. The fabricated switches and connections are designed to minimize routing congestion, and maximize the percentage utilization of the available LUT logic resources (e.g., 90% utilization).

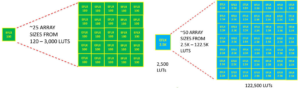

A modular building block is developed, comprised of sets of (hierarchical) LUT’s. Flex Logix offers two blocks, one with 120 LUT’s and one with 2500 LUT’s.

These characteristics of the Flex Logix eFPGA enable the main feature required to accelerate adoption — namely, the embedded IP is available in a very wide range of LUT capacity, intermixing base and DSP functionality.

In Flex Logix terms, the EFLX building blocks are designed to be “tiled together”, with support for a wide range of vertical and horizontal aspect ratios for floorplanning flexibility. Designers can readily build eFPGA IP cores as small as 120 LUT’s to greater than 100K LUT’s. (To simplify the eFPGA tiling implementation, a single clock domain per IP core assumption is made.) SRAM arrays can be compiled, and integrated within the EFLX building block tiles. The number of available building block input and output signals is generous, as well, enabling wide datapath functions to be realized.

EFLX building blocks can be tiled in a wide range of sizes and aspect ratios.

The emergence of eFPGA IP on future SoC’s requires supporting diverse customer requirements for performance, power, computational complexity, and size/cost of the resulting programmable logic core. The architecture of the Flex Logix EFLX offering addresses these requirements, offering both logic and DSP functionality, and a modular “tiled” approach for optimal core area for the target application (with high logic/interconnect resource utilization).

Look for additional articles in the near future describing additional, unique features of the EFLX IP.

For more information on the Flex Logix EFLX product set, please refer to: www.flex-logix.com . There is an excellent introduction to eFPGA technology at: http://www.flex-logix.com/fpga-tutorial/ .

-chipguy

Share this post via:

Comments

0 Replies to “The Year of the eFPGA”

You must register or log in to view/post comments.