I am a believer of continuous improvement in anything we do; it’s pleasant to see rapid innovation in technology these days, especially in semiconductor space – technology, design, tools, methodologies… Imagine a 100K gates up to 1M gates design running at a few hundred MHz frequency and at technology node in the range of .18 to … Read More

Webinar: Samtec and Achronix Expand AI in the Data CenterThe performance demands of data centers continue to…Read More

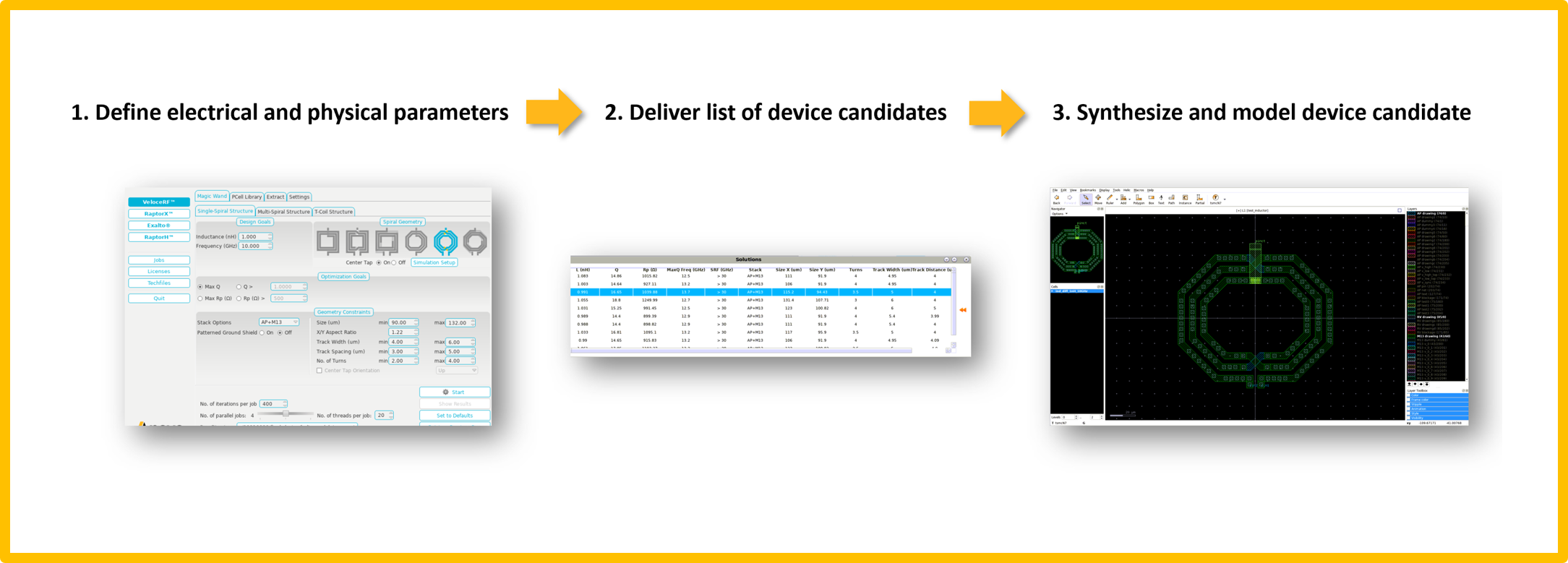

Webinar: Samtec and Achronix Expand AI in the Data CenterThe performance demands of data centers continue to…Read More Don't Settle for Less Than Optimal - Get the Perfect Inductor Every TimeThe meaning of the word “Veloce” is “blazing…Read More

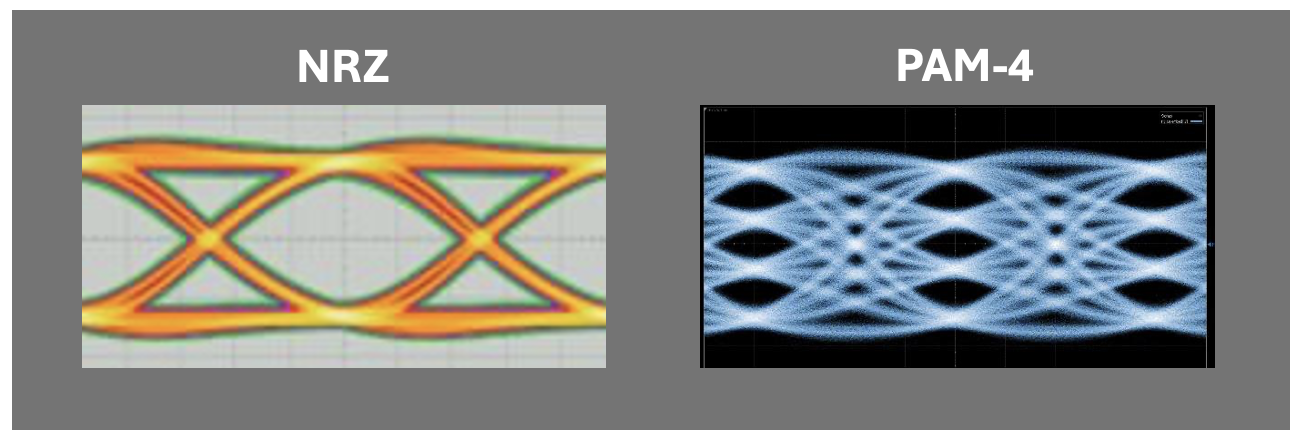

Don't Settle for Less Than Optimal - Get the Perfect Inductor Every TimeThe meaning of the word “Veloce” is “blazing…Read More Synopsys is Paving the Way for Success with 112G SerDes and BeyondData communication speeds continue to grow. New encoding…Read More

Synopsys is Paving the Way for Success with 112G SerDes and BeyondData communication speeds continue to grow. New encoding…Read More An Enduring Growth Challenge for Formal VerificationA high-quality verification campaign including methods able to…Read More

An Enduring Growth Challenge for Formal VerificationA high-quality verification campaign including methods able to…Read MoreDesign Rule Checking (DRC) Meets New Challenges

The traditional batch-oriented DRC process run as a final check to ensure compliance with foundry yield goals is quickly moving toward a concurrent DRC process performed early and often throughout design, especially at the 28 nm and smaller process nodes. What are the technology factors causing this change?

- Increasing number

Fitness Watch Anyone?

I’m an exercise junkie. I’m also not a spring chicken so I like having the time on my wrist. I’ve been anxiously awaiting an iWatch to go with my iPhone 6. As patience is not a virtue of mine, and the iWatch is rumored to be expensive ($400-500). I decided to try a fitness watch.

This is a crowded area that includes activity… Read More

3DIC in Burlingame

Every year in December is what I think of as the main 3D IC conference where you can get up to speed on all the latest. Officially it is called 3D Architectures for Semiconductor and Packaging or 3D ASIP. It is held in the Hyatt Regency in Burlingame (the one right by 101 near the airport). This year it is from December 10-12th.

The first… Read More

Don’t Mess with SerDes!

SerDes stands for Serializer/Deserializer, and SerDes is a serious piece of design, requiring an extremely experienced team of analog engineers (below 10 years’ experience, you’re still a quasi-beginner). Better to rely on an analog guru to draw the SerDes architecture and manage the team! Why does SerDes is becoming more and… Read More

How to Optimize for Power at RTL

Last week I was traveling in Munich attending the MunEDA User Group meetingso I missed a live webinar on the topic of optimizing for power at RTL. I finally got caught up in my email this week and had time to view this 47 minute webinar, presented by Guillaume Boilletof Atrenta. He recommended using a combination of automatic, semi-automatic… Read More

Solution for PI, TI & SI Issues in 3D-ICs

As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

IC Place and Route for AMS Designs

High-capacity IC place and route (P&R) tools can cost $200K and more to own from the big three vendors (Cadence, Synopsys, Mentor), but what about IC designs that are primarily Big Analog and Little Digital? In the EDA world we often have multiple choices for tools, and there are affordable alternatives to place and route out… Read More

Filling the Gap between Design Planning & Implementation

As every other person is talking about IoT today, Michael Munsey of Dassault Systemes looks at this trend in the context of critical success factors and Dassault’s strategy towards providing semiconductor solution that integrates the design chain and continues to keep the semiconductor eco-system healthy and profitable. … Read More

Verification plans overcome hope-based coverage

Coverage is an important yet elusive metric for design verification. It often seems 90% of coverage comes with 10% of the effort, and getting the final 10% covered takes the remaining 90% of a project. Usually, it takes another tool or methodology to get at the 10% the first tool missed. With 100% closure difficult, most teams inspect… Read More

Tools for Chips and Dips an Overview of the Semiconductor Tools Market