OK – I admit I titled this piece as clickbait. There is a core of designers for whom belief in the supremacy of EMACS for RTL creation comes close to religion. Some will read only the title and jump immediately to penning searing comments questioning my intelligence, experience, parenthood and ability to tie my own shoes. Some, I hope,… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More5 of the Top 20 Semiconductor Suppliers to Show Double-Digit Gains in 2016!

Semiconductor Market Researcher IC Insights released an update to the 2016 semiconductor sales forecast which is interesting on many different levels. It really has been an exciting year for the semiconductor industry, absolutely. Two of the stars of this year’s report happen to be two of my favorite fabless companies, Nvidia… Read More

IoT Standardization and Implementation Challenges

The rapid evolution of the #IoT market has caused an explosion in the number and variety of IoT solutions. Additionally, large amounts of funding are being deployed at IoT startups. Consequently, the focus of the industry has been on manufacturing and producing the right types of hardware to enable those solutions. In current … Read More

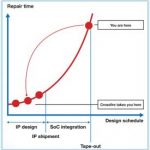

Quality in Hard IP

I was CTO at Atrenta, home of SpyGlass, for many years before the company was acquired by Synopsys, so I know a thing or two about IP quality, to paraphrase a popular commercial. The problem is that even in the best-run IP shops, errors happen. Sometimes they happen on simple changes, especially when you think “This IP has been very … Read More

Tech Industry Analyst Notes On Apple Event

I attended Apple’s special event at the Bill Graham Civic Center in San Francisco and wanted to share with you some of my thoughts and highlights that came out of the event:… Read More

3 in 1 Hardware Verification

Aldec has offered front-end EDA tools for over 30 years but may not be a familiar name to mainstream IC design engineers. That’s probably because for most that period they haven’t really targeted IC design. They have been much more focused on PC-based design for FPGAs particularly where requirements traceability has been important,… Read More

CEO Interview: Chouki Aktouf of Defacto Technologies

As a 30+ year semiconductor veteran I can tell you with 100% certainty that start-ups are the lifeblood of EDA. The mantra is “Innovate or Die!” and that is exactly what Defacto is doing. After more than 10 years of innovating in Design for Test at RTL, Defacto is now offering a complete EDA solution based on generic EDA… Read More

Hotz Tech Crunched

George Hotz, founder of Comma.ai told the world at TechCrunch that he was going to ship a $999 aftermarket autopilot system – the Comma One. The smartphone-sized device was designed to replace the rearview mirror enabling an automated driving experience in appropriately equipped cars – initially certain Acura and Honda models.… Read More

DDoS Attack: A Wake-Up Call for IoT

Welcome to the world of Internet of Things wherein a glut of devices are connected to the internet which emanates massive amounts of data. Analysis and use of this data will have real positive impact on our lives. But we have many hoops to jump before we can claim that crown starting with a huge number of devices lacking unified platform… Read More

The Ramifications of Not Accepting Industry 4.0

In the last couple of years, Industry 4.0 has significantly affected manufacturing on a global scale. With a heavy focus on the Internet of Things, the use of smart machines and other devices has become a critical part of Industry 4.0. With new networks of intelligence on the horizon, there is no doubt that Industry 4.0 will continue… Read More

ASML High-NA EUV is Not Ready for High-Volume Production