Taping out a SoC is never easy. The physical dimensions of the chip often belie the work which has been done to get to the tapeout stage. And it is still not a done deal as the hardware and software development teams await the arrival of the test chip from the foundry to complete the post silicon bring-up and validation. The pressure on the design team is telling, more so due to the possibility of the chip not functioning as desired. A failing test chip brings up the prospect of potentially missing the market window and taking a hit on the cost incurred owing to the high NRE cost in the case of lower process nodes and missed schedules.

In most cases, the development of the SoC or IP is the handiwork of dedicated design teams spread across multiple locations, and collaborating using in-house design flows for their EDA tools. The efficiency of design flows employed within the design companies plays a very critical part to successful tapeouts. Enterprises which have this secret sauce manage to successfully tapeout time and again. These design companies have integrated their design tool flow between the EDA tools, with flow automation and efficient design handoffs. Seamless exchange of the design data between the software, hardware and verification teams enables the engineers to work in tandem and engage in productive collaboration. Ensuring reusablity and using a single source to automatically generate the desired correct-by-construction collateral consumed in various formats by different team members pays rich dividends and helps shorten the design development cycle. An additional benefit of this approach is that it mitigates the possibility of mis-interpretation of data or developing code based on an incorrect version of the collateral such as the memory map. It also reduces the effort otherwise spent on manually developing the desired code and verifying the same.

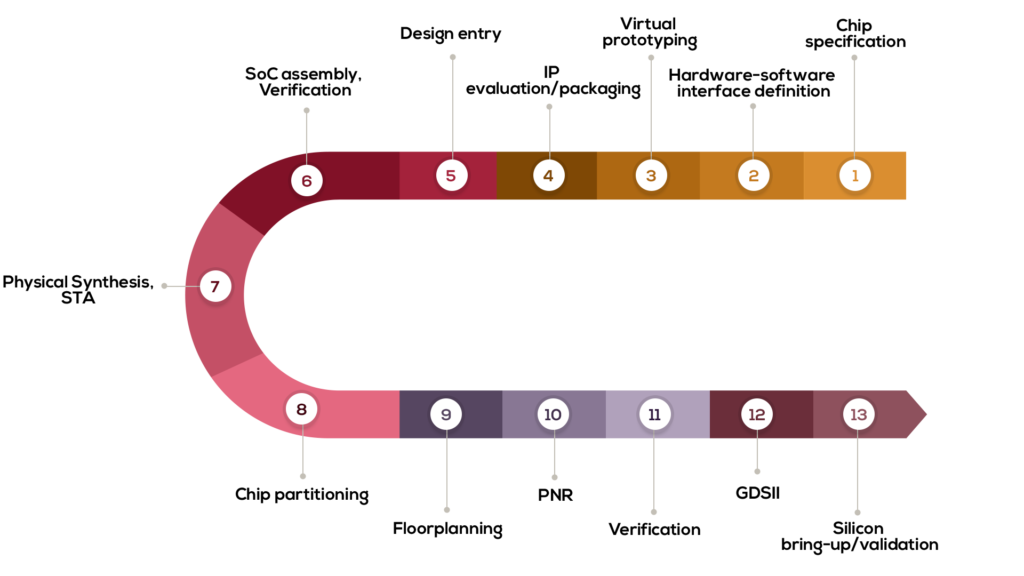

The importance of a good flow and efficient collaboration between the different teams becomes even more significant today during the current pandemic and a potential economic downturn rivaling the Great Depression. Setting up a design flow and automating as far as possible helps in performing well defined, potentially mundane tasks which are prone to human error. These include for example, virtual prototyping, generation of structural RTL for top level wiring, insertion of test logic, documentation, design handoffs and creation of testbench and test vectors to verify the design. So, what are some of the key ingredients of developing a flow, which increases the possibility of successful tapeouts?

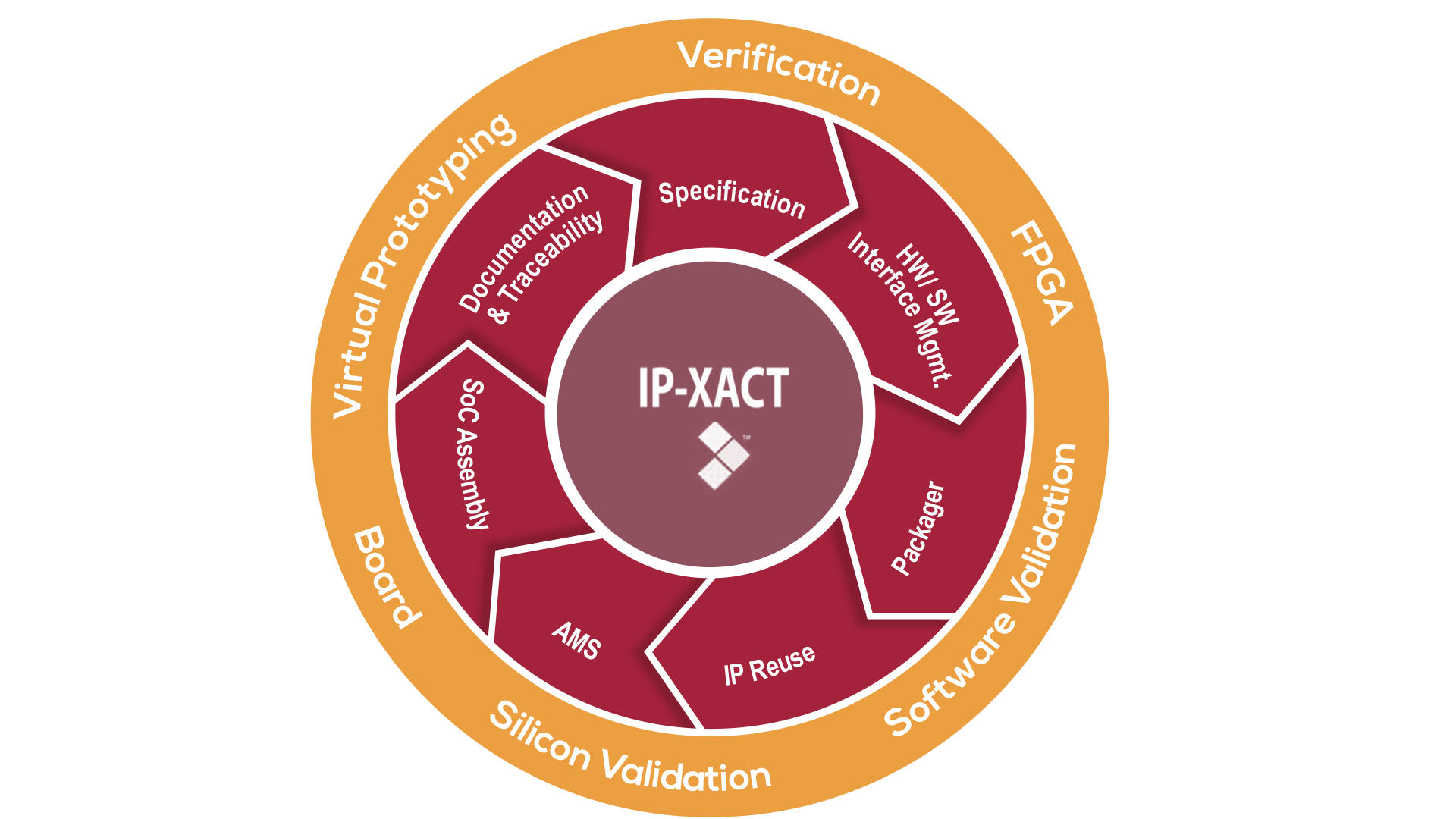

One of the key ingredients for most of the recipes deployed by companies in developing a successful design flow is a good data model, malleable enough to be used for automating the different nuances of the complex design flows of today. While some companies prefer using proprietary data models alongside Perl/Tcl/Python scripts, a number of companies have opted for using IP-XACT. There are a number of advantages of using IP-XACT as a base for the design flows. Some of these are listed below:

- It is an IEEE standard which implies it is open and accessible to all. Dependence on proprietary methods to develop design flows, can impose restrictions in modifying them as and when needed.

- It comes equipped with a standard API which can be used to customize solutions by complimenting the IP-XACT description with a layer of software.

- Using the API, embellishes the value proposition of the generators. It can be used to capture the configuration intelligence within the generators to automatically generate the final configured IP-XACT description of an IP.

- It is extremely flexible, works with huge legacy systems and yet can be applied to projects that have no legacy IP.

- IP-XACT standardizes a number of different meta-data specifications and provides a tight generator interface (TGI) to provide programmability.

- Distributed software and hardware teams can use IP-XACT to collaborate more efficiently and exchange design information quickly between different design environments.

- It pulls together different EDA tools from multiple vendors into a single integrated design and verification environment.

It is a given for most chips developed these days to have a software component associated with it, to control and manage its operation. The first step in any SoC development cycle involves the creation of the design specification. But with the growing importance of safety critical systems in industries such as automotive, aerospace, defense etc., a number of designs have an associated set of requirements typically captured using ReqIF (Requirements Interchange Format) where put simply, every requirement should be tied to a specific part of the design. This set of requirements defined using ReqIF, is then used to automatically seed the design specification. The associated documentation that is generated as a result, eventually feeds into the overall design documentation. This brings into play, the notion of design traceability, something which is growing in relevance in the SoC designs of today and maintained throughout the design flow.

Along with the crystallization of the design specification seeded through a set of requirements, the reality is that the hardware-software memory map also gets developed in tandem. This memory map along with the architectural specifications forms the common source for the starting point in the design flow. Different outputs such as structural RTL, C header files, System C files are generated automatically to ensure that the design prototype is verified and confirmed to work as expected. This is an iterative flow and any changes required downstream in the design cycle is validated in the prototype and the necessary outputs generated for use downstream. This approach ensures that all the teams are using the same version of the outputs generated leaving little scope of misinterpretation of specifications. An additional benefit of this approach is that it enables the verification team to validate the results at different stages of the flow and ensures that the results are consistent across the flow.

While everyone agrees with the benefits of a good design flow, it is useful to consider the importance of flow automation from another perspective. Aberrations in any SoC development cycle is often caused due to design modifications such as changes to the functionality, modifications to memory map etc. or due to problems which can creep in at any step of the design flow. With increased design complexity and dispersed design teams, it becomes important to keep everyone in sync, something which is critical in keeping a design on track. Design engineers have often been guilty of making the necessary design changes locally, and then failing to inform other engineers about the changes made to the design. The ramification of this faux pas is often felt late in the design cycle. To resolve this issue, it becomes important to ensure that the changes are made at the design architecture stage and post validation, proliferated to all the teams to keep the numerous models – architectural, TLMs, software, power and RTL, documentation etc. in sync.

The next step in most design flows involves defining the top level of the SoC along with the power and timing constraints. Defining the top-level partitions, their pins, and their interconnect is something which can be done using several methods instead of a manual approach. A number of companies use different approaches for this, but a common thread involves using custom Tcl, Python or Perl scripts along with a proprietary data model to define the interconnect. While custom scripts have helped to considerably boost the automation of design flows, their productivity gets severely limited when design teams have to modify the scripts in order to adapt to different design constraints or integrate with unfamiliar 3rd party IPs. As a result, of late, a number of companies have abandoned this approach and are migrating to using IP-XACT. This approach eases the pain involved in manually creating the interconnect, making modifications, ECOs and eliminating connectivity errors while retaining the flexibility to automatically generate the RTL in different languages. For each of the partitions defined at the top level, the IPs – either 3rd party or internal IPs are packaged if needed, qualified and wired either to other IPs or to black boxes (any yet-to-be-developed design module) using methods similar to the integration of the top level as described above. Using IP-XACT solutions instead of custom scripts, provides the ability for designers to integrate IPs from multiple suppliers and verify that IP in-situ with a variety of leading edge verification tools, such as protocol checkers, design rule checkers, clock & reset domain crossing analysis, static timing and formal verification tools, embedded software testing etc.. A large part of the outputs needed for these tasks are automatically generated thereby ensuring a common reusable flow.

Having a reusable connectivity solution provides design teams with several benefits. Some of them are captured below.

- Quickly build a correct-by-construction platform-based design by adding the necessary components and interfaces, making modifications easily as needed.

- Flexibility in implementing design through a bottom-up design or top-down design flow or a combination of both.

- Easily package legacy RTL as an IP-XACT compliant IP and wire as needed in your design.

- Provides a method to keep track of the various versions of an IP being used in the design, and if the latest version does not work, always fall back to an older version.

- Ability to connect design instances by using a common bus or a custom interface thereby reducing the total number of connections in a design.

- Minimize the scope of making errors while connecting IP instances.

- Manage modifications to logical design hierarchy based on the physical design requirements while considering timing and power constraints.

- Manage IPs, SoCs configurations/re-configurations easily as needed and netlist the design in the desired format such as Verilog, VHDL, System Verilog or System C.

- Create better workflows through efficient design handovers in-between design teams.

- Generate documentation automatically in different formats such as pdf, MS Word, Dita, html etc. This becomes particularly important as a number of things change in the design cycle during the hardware-to-software iterations which often causes the design documentation to be out of sync with the changes made. Automatic document generation ensures that the documentation is always current and in-sync with the design changes.

Each of these partitions or blocks defined at the top level, comes with its timing budget and power estimates which needs to be met and serve as guidelines for the construction of the design partition or top-level blocks. These constraints may change due to roadblocks found during design implementation or architectural changes, but a flow such as this enables a quick iteration by making changes at the design specification stage and then automatically generating the outputs needed for the downstream flow and tools.

Talking about the design flow with IP-XACT would be incomplete without mentioning about the PPA (Power-Performance-Area). Meeting the PPA is a critical requirement for all designs and is often prone to long iteration cycles from manually modifying the RTL to long tool runtimes. To find a suitable solution, successful design flows empower design teams to try various what-If scenarios to create the design hierarchy best suited to meet the PPA during physical implementation. Some of the features included in such flows are

- Ability to modify logical hierarchy while automatically generating RTL in the desired language. Logical restructuring features include

- Grouping instances at the same level of hierarchy into a new hierarchy or ungroup a hierarchy as needed.

- Moving an IP or sub-system from one hierarchy to another.

- Creating feedthroughs or re-route nets as needed while preserving existing connections and memory maps during hierarchy manipulation.

- Define multiple design hierarchies without actually modifying the actual design hierarchy.

- Manage timing and power constraints effectively for the different hierarchy.

- Select which hierarchy produces the best results for timing closure.

To hasten the process of developing the SoC or IP using well defined flows, it becomes necessary to use solutions which are tried and tested and is part of a production flow in several companies. For more information on how to automate your design flows and build your designs faster, visit www.magillem.com.

Magillem customers include the top 20 semiconductor companies worldwide.

Magillem is a pioneer and the leading provider of IP-XACT based solutions aimed at providing disruptive solutions by integrating specifications, designs & documentation for the semiconductors industry. Using the solutions provided by Magillem, design companies can automate their design flows and successfully tape-out their designs faster at a reduced cost.

Magillem is one of the leading authorities on IP-XACT standard. It is also the Co-chair of the IP-XACT 2021 Accellera committee and an active member since the inception of the IP-XACT standard.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.