Taping out a SoC is never easy. The physical dimensions of the chip often belie the work which has been done to get to the tapeout stage. And it is still not a done deal as the hardware and software development teams await the arrival of the test chip from the foundry to complete the post silicon bring-up and validation. The pressure on… Read More

Tag: soc interconnect

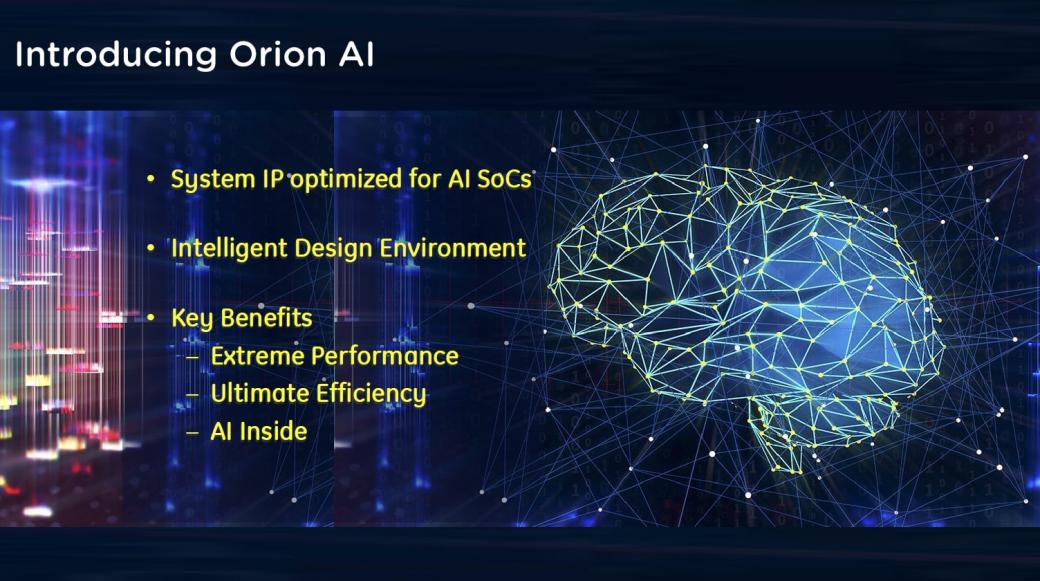

Leveraging AI to help build AI SOCs

When I first started working in the semiconductor industry back in 1982, I realized that there was a race going on between the complexity of the system being designed and the capabilities of the technology in the tools and systems used to design them. The technology used to design the next generation of hardware was always lagging… Read More

Is Interconnect Ready for the Post-mobile SoCs?

The interconnect technology is one of the unsung heroes of the system-on-chip (SoC) revolution. It’s the on-chip networking fabric that is used to link various IP cores on an SoC floorplan. The technology facilitates links between multiple processors, on-chip memories, hardware accelerators and more. In other words,… Read More

Automating Timing Closure Using Interconnect IP, Physical Information

Timing closure is a “tortoise” for some system-on-chip (SoC) designers just the way many digital guys call RF design a “black art”. Chip designers often tell horror stories of doing up to 20 back-end physical synthesis place & route (SP&R) iterations with each iteration taking a week or more. “Timing closure”, a largely… Read More