The life of a SoC designer is an unenviable one. Not only does he have to work in a landscape where competition is intense but he also has to collaborate effectively with globally dispersed teams to ensure the design meets the project timeline. Then there are also the risks, more so in the current pandemic! There is the constant fear of a dead chip on arrival or issues found post silicon or the tape-out slipping beyond the due date which can have widespread ramifications. As part of a multi-pronged strategy to mitigate the risks as well as build designs faster, a large number of companies have slowly but steadily moved towards using verified third-party IPs, for parts of the design which is not in their core competency.

However, this trend of incorporating more and more third-party IPs in an SoC is not without its share of problems. The complexity of IP configurations now is no longer easy to manage manually and requires an infrastructure which is capable of tracking the configurations throughout the product life cycle. The tight marriage required between the hardware and software teams to provide state-of-the-art SoCs of today adds yet another dimension to the challenges faced by the designers. The need for a methodology to build, update and configure IPs appropriately is felt more so than ever. While there are some software solutions which address this aspect of the problem to some extent, their reliance on proprietary technologies and inability to coexist with legacy flows poses a problem for a large number of companies.

Over the last half decade, companies have slowly embarked on an effort to addressing these issues and automating flows while relying on standards as an underlying infrastructure and ensuring a common data-model which can be leveraged between all the teams.

It is no mere coincidence that most enterprises have chosen IP-XACT as the underlying standard to base their infrastructure for developing automated flows.

What is IP-XACT?

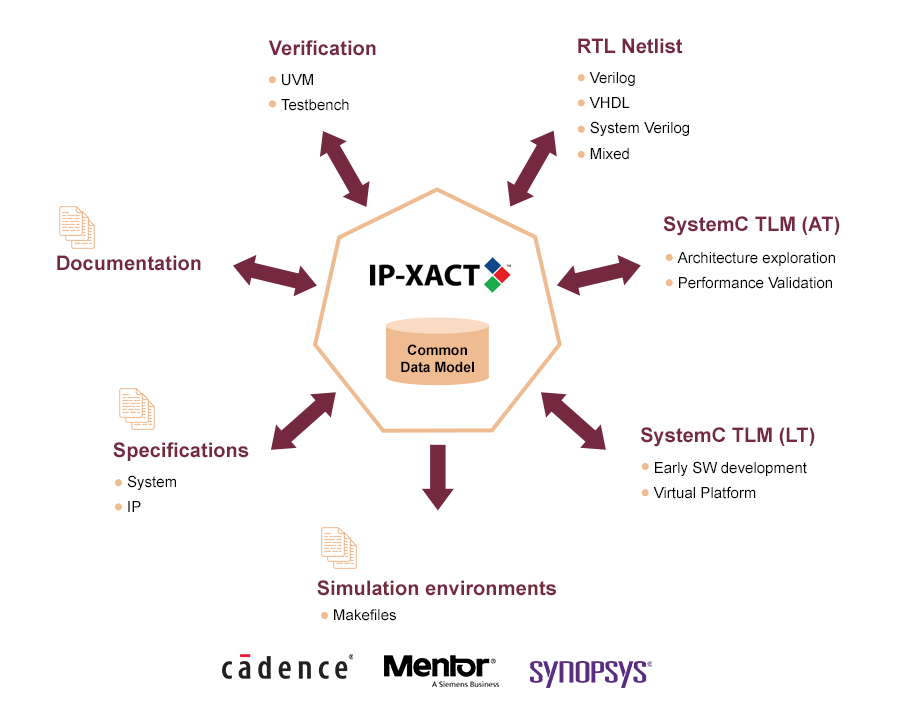

IP-XACT, first released by the SPIRIT Consortium, is a standard developed with the sole objective of promoting reusability of IPs within the design community. It enables IP providers to provide a singular description of their IPs which is both readable and machine processable for both components and designs, and share it with the IP users packaged along with the desired collateral. IP-XACT also describes system designs and the interconnection between the IPs along with other details such as address maps, interfaces etc. providing a common design representation that can be used by IP vendors, design integrators and EDA tool providers to exchange within their flows.

IP-XACT became an IEEE standard in 2009 and is published as IEEE-1685. While a number of companies started using it even before it became an IEEE standard, the usage started increasing in the last few years as more and more companies realized the potential it offered in helping create and automate their custom design flows.

Why the sudden increase of interest in IP-XACT?

With a lot riding on the SoCs of today, both small and large semiconductor companies alike, are heavily invested in the common goal of ensuring successful tape-outs within the scheduled timelines. Any delays or snags in the design flow can potentially impact both their time-to-market as well as the company bottom line.

Most design teams have attempted to resolve this issue by working in parallel on several fronts and investing heavily on block and system-level verification. For example, top level and block level design integration of designs is done in parallel to the development of RTL and verification environment. But this approach is not the most optimal often requiring more resources and prone to manual errors.

Another issue which designers face involves the EDA tools produced by a number of vendors, many of which use unique and proprietary formats. Developers are often posed with the problem of identifying ways to exchange the design information efficiently between different design environments.

One way to resolve this and ensure timely and successful tape-outs is to provide for a solution, which encompasses at the very least:

- A well-defined design methodology suited for your custom requirements and EDA tools of your choice

- Efficient design collaboration between design teams sometimes dispersed across geographical boundaries especially between hardware & software teams

- Leverage IP reuse for internal and third-party IPs

- Design flow automation which ensures

- Faster design integration

- Selecting the correct configuration of IPs

- Smooth exchange of design information between different tools and ensuring design handoffs between teams

- Avoiding misinterpretation of design specifications such as register maps

- Automatic generation of RTL and other collateral such as C header files, memory maps, UVM models, documentation etc.

In the past, companies have tried to address some of these problems, by creating solutions based on either custom scripts, proprietary technology or a combination of both. The challenge with this approach has been that the solution needs to be constantly maintained and tends to fall apart when the engineers managing the solution leave the company. The ability to integrate design flows by creating custom generators to pilot EDA tools and back annotate the results has resulted in companies now taking a hard second look at IP-XACT to serve as the underlying vehicle for their tooling solutions. IP-XACT stands out in being an IEEE standard, which means that companies no longer have to worry about maintaining or enhancing any proprietary infrastructure. By providing a standardized data exchange format, IP-XACT has the flexibility to represent multiple companies’ requirements and the hooks to allow design information to be automatically extracted and used in flow automation and advanced verification.

One of the important cornerstones of the IP-XACT standard is its capability of packaging a design into an IP-XACT component. The component description includes among other things, the specification of the periphery of each IP block along with the bus interfaces, physical signals, their mapping to logical bus interfaces, configuration, address blocks, register descriptions, filesets and documentation information. The information contained in the description can be used by designers to automatically integrate the correct configuration of IPs and construct the SoC faster in a single integrated design and verification environment while mitigating the possibility of any errors being introduced in the design.

An inherent advantage of using IP-XACT is that it not only helps in improving the IP ecosystem within a company as design teams can easily package a design along with the necessary collateral, but its use as a common data model also enables distributed teams to collaborate more efficiently and exchange design information quickly between different design environments. IP-XACT also comes equipped with a standard API which can be used to customize solutions even further by complimenting the IP-XACT description with a layer of software. For example, the API could be used with an EDA tool to actually interface into a customer flow by leveraging the design information available in the IP-XACT database. Using the API, embellishes the value proposition of the generators and can be used to capture the configuration intelligence within the generators to automatically generate the final configured IP-XACT description of an IP. This capability is of immense value to an IP provider as it enables a precise and controlled use of the selected configuration.

The versatility of the IP-XACT standard and its ability to coexist and work with other systems including legacy ones used for IP reuse and flow integration, makes it the perfect choice for many a company.

Advantages of using IP-XACT

One of the most important aspects of IP-XACT is that it is an IEEE standard backed by leading semiconductor companies who are heavily invested in utilizing it for tooling purposes as well as IP reuse. The fact that it is developed keeping IP reuse in mind, makes it ideal to build IP ecosystems within an enterprise.

Design teams can leverage this ecosystem by using it to create more IP sub-systems and SoCs. To assemble the designs faster, designers can use the connectivity features defined in IP-XACT to quickly create an interconnect fabric for their designs and utilize the register maps of the IPs to compute the full system memory map of the design. Designers can also use the design database to create generators such as s/w C header files, netlist in VHDL, Verilog, System Verilog or System C, UVM models, testbenches, documentation etc.

One of the lesser known advantages of IP-XACT and one of the most important capabilities is that it can be used extensively for tooling purposes and automating the flows, something which a number of companies have started to capitalize on of late.

Some of the other capabilities which IP-XACT possesses includes

- IP-XACT is designed for IP reuse

- Faster and easier system integration

- Support for multiple layers of abstractions (designs and protocols) enables integrators to quickly create the top level for the designs.

- Built in error checks reduces the possibility of errors

- Extensibility to add design and flow information

- With support for features such as views/fileSets,, managing deliverables becomes simple and fully automated process.

- Support for design traceability which is a key requirement for ISO 26262 certification

A standard does not have to be perfect but if there are enough people adopting it over time, it can be considered to be a good standard. This applies to IP-XACT as well. With the number of companies adopting the standard increasing steadily, there is no doubt that the standard is here to stay.

Finding the right solutions

To hasten the process of developing the SoC or IP, it becomes necessary to use solutions which are tried and tested and is part of a production flow in several companies. For more information on how to build your designs faster, visit www.magillem.com. Magillem customers include the top 20 semiconductor companies worldwide.

Magillem is a pioneer and the leading provider of IP-XACT based solutions aimed at providing disruptive solutions by integrating specifications, designs & documentation for the semiconductors industry. Using the solutions provided by Magillem, design companies can automate their design flows and successfully tape-out their designs faster at a reduced cost.

It is one of the leading authorities on IP-XACT standard. Magillem is the Co-chair of the IP-XACT 2021 Accellera committee and an active member since the inception of the IP-XACT standard.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.