Back in the 1970s we did Layout Versus Schematic (LVS) checks manually, so when internal EDA tools arrived in the 1980s it was a huge time saver to use LVS in finding the differences between layout and schematics. One premise before running LVS is that both layout and schematics are complete and ready for comparisons. Fast forward to today, SoC design sizes can number in the billions of transistors. If a design team waits until signoff verification to start running LVS, then the first runs would report way too many errors and then that would then create many iterations to fix the errors, tending to delay the project.

The clever engineers in the Calibre team at Siemens have developed an approach that allow engineers to start running LVS much earlier in the design process, even when netlists are not completed. With the Calibre nmLVS Recon Compare tool you can start running early LVS comparisons, saving valuable time and effort.

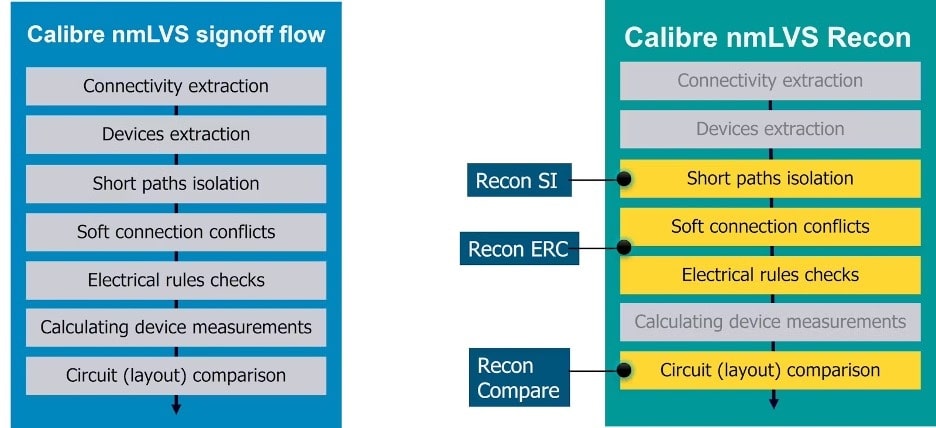

This tool automates two things: incomplete blocks are black-boxed, and ports are mapped automatically. The traditional Calibre flow and Recon flows are compared below, to highlight the four areas where Recon comes into play:

Using the Recon flow your verification engineers can find and fix early circuits that are not finalized. Marvell used this flow and presented at the annual User2User Conference earlier this year, watch that online. Users have reported an average 10X improvement in run times, plus 3X less RAM requirements when using Calibre nmLVS Recon.

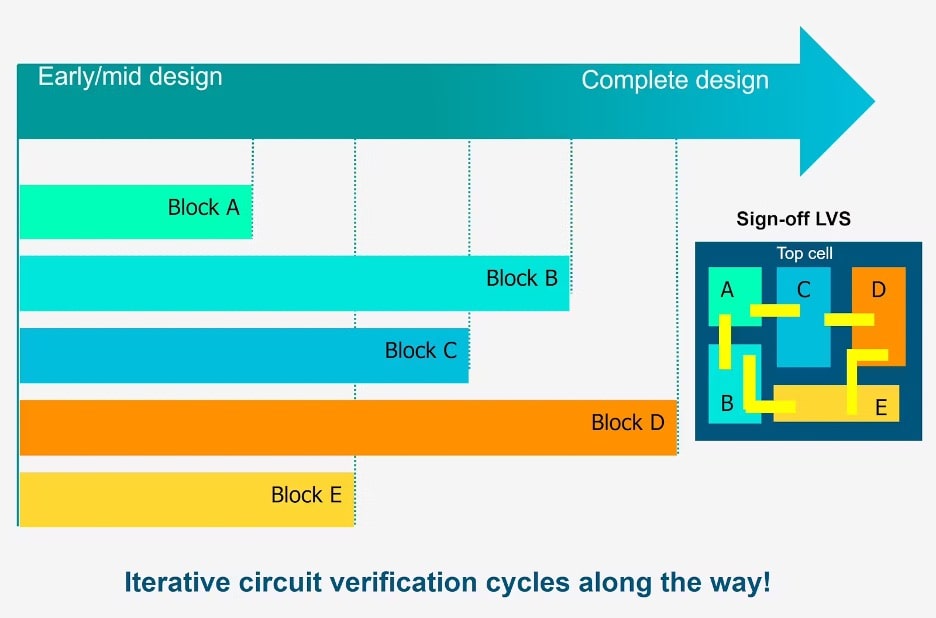

Large IC design teams divide up the work to conquer the project, and each block designed is typically in a different state of completion. Simply waiting for all blocks to be equally complete before running any LVS results in long project delays. You really want to start checking top-level connectivity early in the project to avoid delays and fix connectivity issues earlier. With the Recon methodology you are running early LVS at multiple points throughout the complete design phase, instead of just at the end.

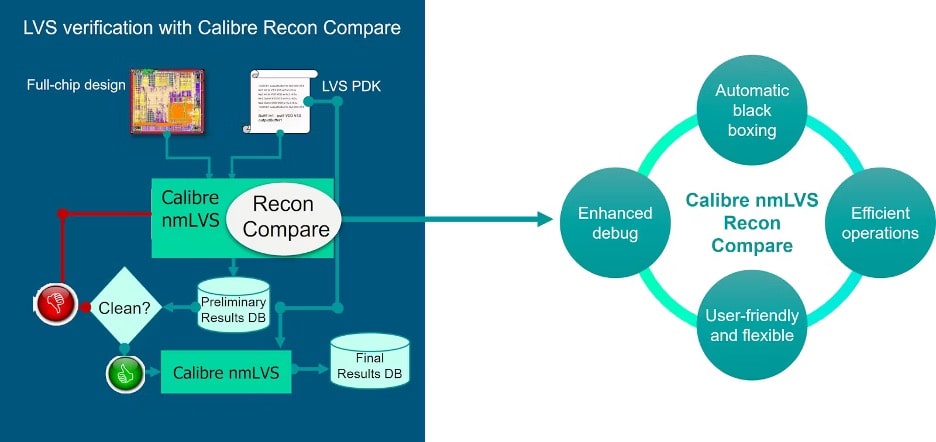

Black Boxing

Incomplete blocks are automatically marked for black boxing, so that their internal details are not traced or compared, only the inputs and outputs to the block. This approach finds interconnect issues between the blocks more quickly.

Port Mapping

Ports on each block are automatically mapped between layout and schematics, so there’s consistency. Mapping knows how each block connects to all other blocks, even when details inside of a block are incomplete.

Comparison Engine

Both black boxing and mapping are done first, then Calibre nmLVS Recon Compare will evaluate layout and schematic info. If there are any missing connections or mismatched components, they get reported.

The Recon Compare flow is detailed below, and the tool reads input data and quickly completes through its smart logic.

An intuitive UI lets you specify comparison parameters and then see the results, so that you can find and fix any LVS errors.

Your IC design team benefits from using this Recon Compare by identifying LVS issues much earlier in the design process, so that you reach full-chip LVS clean much quicker than waiting for all blocks to be completed. Start running Recon Compare as soon as you have the first top-level of interconnect defined. Each design team working on their blocks will know sooner if there are any port connectivity issues. Reaching your goal of LVS clean happens sooner with this shift-left methodology, giving you higher confidence of first-silicon success.

It’s a best practice to run Recon Compare with your version control system, so that you track all revisions to each block.

Summary

LVS tools have been around since the 1980s, yet today’s large SoCs require updated methodologies in order to reduce turn-around-time (TAT), and ensure that schedules are met. Calibre nmLVS Recon Compare is a new approach that uses black boxing and port mapping that make early LVS runs on designs with incomplete blocks possible.

This shift-left approach has verification engineers running LVS much earlier in the project to find and fix connectivity errors more quickly than before. Debugging the LVS errors is intuitive, saving you time. Read the complete White paper online.

Related Blogs

- What are Cloud Flight Plans? Cost-effective use of cloud resources for leading-edge semiconductor design

- 3DIC Verification Methodologies for Advanced Semiconductor ICs

- Design Stage Verification Gives a Boost for IP Designers

- Optimizing Shift-Left Physical Verification Flows with Calibre

Comments

There are no comments yet.

You must register or log in to view/post comments.