Networks-on-chip (NoCs) are very configurable, arguably the most configurable piece of IP that you can put on a chip. The only thing that comes close are highly configurable extensible VLIW processors such as those from Tensilica (Cadence), ARC (Synopsys) and CEVA but Sonics would argue their NoCs are even more flexible. But … Read More

Tag: verification

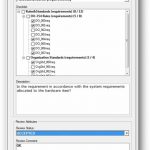

If requirements ask for it, it had better be there

Engineers are known for their attention to detail and precision in thinking, but sometimes still struggle during compliance audits. This is especially true the longer a list of requirements becomes, especially unstructured lists kept in spreadsheets and on Post-It notes.

It gets even more complicated, because in defense circles… Read More

Have you Tried ALDEC?

I must admit. I was too comfortable. Let me explain, I’m a ModelSim guy from Mentor Graphics. I did not really think nor care much of the other RTL simulator options. How could someone build a better tool with respect to simulation? Let me introduce you to Aldec. Aldec was founded in 1984 by Dr. Stanley M. Hyduke. 30 years later they are… Read More

JasperGold COV App, the Swiss Army Knife for Verification

At the Jasper Users Group meeting in October Rajeev Ranjan presented on the JasperGold COV App which he described as the Swiss army knife for verification. It comes in many sizes and contains many useful tools.

The primary goal of COV is to provide coverage metrics:

- stimuli coverage: how restrictive is the design behavior under

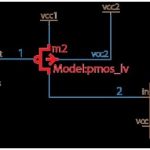

How to Simplify Complexities in Power Verification?

With multiple functionalities added into a single chip, be it a SoC or an ASIC, maintaining low power consumption has become critical for any design. Various techniques at the technology as well as design level are employed to accomplish the low power target. These include thinner oxides in transistors, different sections of … Read More

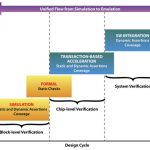

Assertions verifying blocks to systems at Broadcom

Speaking from experience, it is very difficult to get an OEM customer to talk about how they actually use standards and vendor products. A new white paper co-authored by Broadcom lends insight into how a variety of technologies combine in a flow from IP block simulation verification with assertions to complete SoC emulation with… Read More

Cadence’s System-to-Silicon Verification Summit

At this year’s DAC, I spoke with several friends at Cadence. I got the distinct impression that something at Cadence had changed. There was a sense of pride and accomplishment that it seems to me had drifted away over the years. Now employees were speaking with true conviction about the accomplishments of the product development… Read More

Cadence Introduces Palladium XP II

Well, despite all the arguments in the blogosphere about what process node palladium’s silicon is, and whether the design team is competent, and why it reports into sales…Cadence has announced their latest big revision of Palladium. Someone seems to be able to get things done. Of course it is bigger and faster and … Read More

Debugging Verification Constraints

In his DAC keynote last year (2012) Mike Mueller of ARM compared how much CPU was required to verify the first ARM versus one of the latest ARM Cortex CPUs. Of course the newer CPU is hundreds of times larger than the first ARM but the amount of verification required was millions of times as much, requiring ARM to construct their own datacenter… Read More

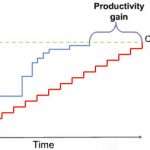

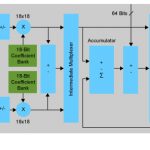

The fixed and the finite: QoR in FPGAs

There is an intriguingly amorphous term in FPGA design circles lately: Quality of Results, or QoR. Fitting a design in an FPGA is just the start – is a design optimal in real estate, throughput, power consumption, and IP reuse? Paradoxically, as FPGAs get bigger and take on bigger signal processing problems, QoR has become a larger… Read More