In working with TSMC and GlobalFoundries on AMS design reference flows I have experienced first hand the increasing verification challenges of nanometer analog, RF, and mixed-signal circuits. Tools in this area have to be both silicon accurate and blindingly fast! Berkeley Design Automation is one of the key vendors in this … Read More

Tag: verification

What changes to expect in Verification IP landscape after Synopsys acquisition of nSys?

Even if nSys acquisition by Synopsys will not have a major impact on Synopsys’ balance sheet, it is a kind of earthquake in the Verification market landscape. After the Denali acquisition by Cadence in 2010, nSys was most probably the market leader in verification IP, if we look at the independent VIP providers (excluding Cadence).… Read More

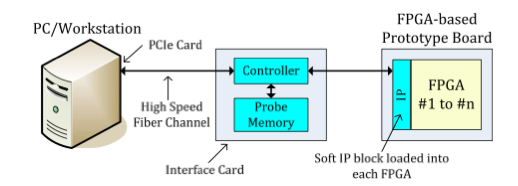

Speeding Verification of FPGA Prototype Boards

It is no secret that SoC designs continue to increase in complexity and time-to-market windows are shrinking. While there is room for debate on just how big a fraction of SoC design effort goes on verification, there is no debating that it is a large part of the total. Simulation is increasingly too slow, especially when software … Read More

Cache Coherency and Verification Seminar

At DAC Jasper presented a seminar with ARM on cache coherency and verification of cache coherency. The seminar is now available online for those of you that missed DAC or missed the seminar itself.

Cache architectures, especially for multi-core architectures, are getting more and more complex. Techniques originally pioneered… Read More

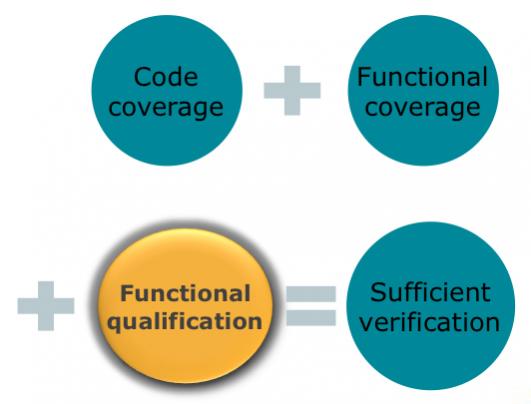

How Good is Your Verification?

The traditional way for analyzing the effectiveness of testing in the software world and in the RTL world is code coverage. Make sure that every line of code is executed. This is a pretty crude measure since even 100% code coverage doesn’t mean that all the condition has really been tested but it is certainly necessary–after… Read More