You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

SpringSoft, soon to be part of Synopsys but officially still a separate company for now, just announced that Laker[SUP]3[/SUP], the third generation of their layout product family, is featured in TSMC’s 20nm Custom Reference Flow.

Laker 20nm advancements include new double patterning-aware design and voltage-dependent… Read More

Today GlobalFoundries announced a 14nm process that will be available for volume production in 2014. They are explicitly trying to match Intel’s timeline for the introduction of 14nm. The process is called 14XM for eXtreme Mobility since it is especially focused on mobile. The process will be introduced just one year after… Read More

Cadence at 20nmby Paul McLellan on 08-21-2012 at 8:10 pmCategories: Cadence, EDA

Cadence has a new white paper out about the changes in IC design that are coming at 20nm. One thing is very clear: 20nm is not simply “more of the same”. All design, from basic standard cells up to huge SoCs has several new challenges to go along with all the old ones that we had at 45nm and 28nm.

I should emphasize that the paper… Read More

Twenty eight nanometer is progressing very well. Our output and our yields are both above the plans that we set for ourselves and the plans that we communicated to our customers early in the year. Early in the year means January-February of the year, we set our plans in output and in yields and we, of course, ever since then we tried to… Read More

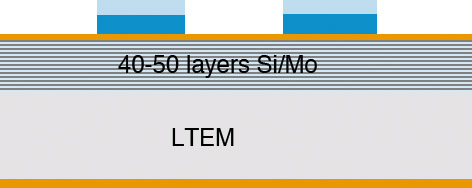

EUV Masksby Paul McLellan on 07-17-2012 at 11:00 pmCategories: Uncategorized

This is really the second part to this blog about the challenges of EUV lithography. The next speaker was Franklin Kalk who is CTO of Toppan Photomasks. He too emphasized that we can make almost arbitrarily small features but more and more masks are required (not, that I suspect, he would complain being in the mask business). For EUV… Read More

What does mango beer have to do with semiconductor design and manufacturing? At a table of beer drinkers from around the world I would have never thought fruity beer would pass a taste test, not even close. As it turns out, the mango beer is very good! Same goes for 20nm planar devices. “Will not work”, “Will not yield”, “Will not scale”,… Read More

Everyone knows Moore’s Law: the number of transistors on a chip doubles every couple of years. We can take the process roadmap for Intel, TSMC or GF and pretty much see what the densities we will get will be when 20/22nm, 14nm and 10nm arrive. Yes the numbers are on track.

But I have always pointed out that this is not what drives… Read More

On Wednesday there is a User Track Poster Session that examines the design impact of process variation in GLOBALFOUNDRIES 28nm technology. For those of you who are wondering what process variation looks like at 20nm take this 28nm example and multiply it by one hundred (slight exaggeration, maybe).

Variation effects have a significant… Read More

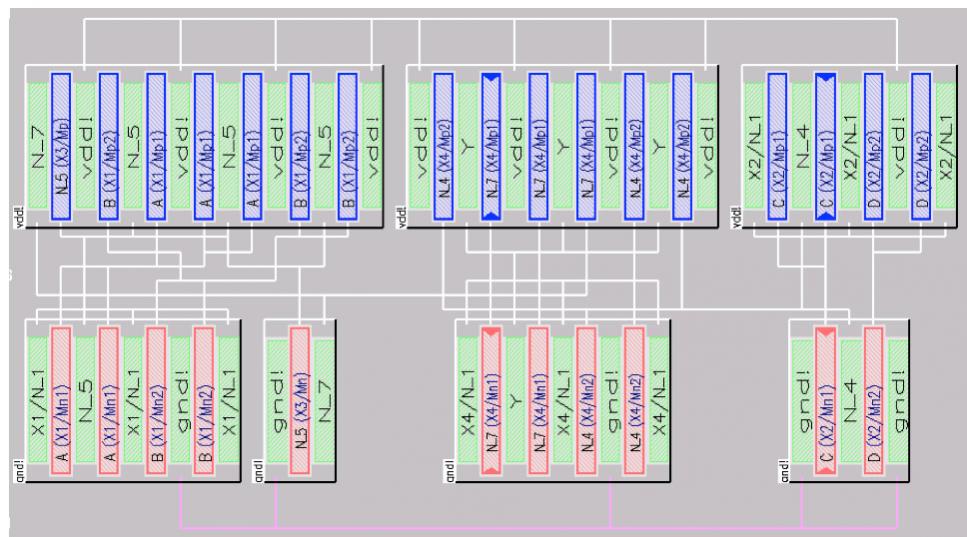

As I mentioned in my blog GlobalFoundries Update 2012, the GFI people are on the move at DAC 2012. Here is a little more detail on the up and coming AMS and Digital reference flows for 28nm and 20nm.… Read More

The introduction of 28nm high-volume production for IC semiconductor devices will usher the era of “extreme low-k1” manufacturing, i.e. the unprecedented situation in the long history of the silicon technology roadmap, where computationally intensive (and EDA-driven) Design-Technology Co-Optimization will become the… Read More