Analog IC designers are gradually adopting what digital IC designers have been doing for years, metric driven verification. When you talk with analog designers about their methodology and approach, you hear terms like artisan being used which implies mostly a manually-oriented methodology. Thanks to automation from EDA companies,… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read MoreHow to Assure Quality of Power and SI Verification?

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

A Brief History of ARM Holdings

It was on 26th April 1985 (at 3pm to be precise) that the very first ARM silicon sprang in to life – it was a 25K transistor design implemented in 3um technology with just 2 layers of metal.

However back then the “A” in ARM stood for Acorn – ARM the company had yet to be formed. Acorn sold computers to schools and so cost… Read More

The Leading Edge Depends on What You Are Doing

At Semicon Japan a few days ago, Subi Kengeri of GlobalFoundries delivered the keynote. While he covered a number of topics, using Tokyo’s recent win of the 2020 Olympics as a hook, one major theme was the increasing importance of processes other than the bleeding edge digital processes that get all the news.

What is leading… Read More

Virtual Prototypes Made Easier for SoC Design

Using a virtual prototype for your SoC design is accepted, conventional wisdom today because it can save development time by eliminating design iterations and avoid costly bugs that will cause an expensive product recall. In order to simulate your virtual prototype you need models, so a major question has always been, “Where… Read More

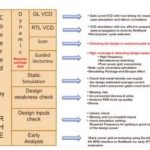

Physically Aware Synthesis

Yesterday Cadence had their annual front-end summit, the theme of which was physically aware design. I was especially interested in the first couple of presentations about physically aware synthesis. I joined Cadence in 1999 when they acquired Ambit Design Systems. One of the products that we had in development was called PKS… Read More

What Makes A Designer’s Day? A Bottleneck Solved!

In an environment of SoCs with tough targets of multiple functionalities, smallest size, lowest power and fastest performance to achieve within a limited design cycle window in order to meet the rigid time-to-market requirements, any day spent without success becomes very frustrating for a designer. Especially during tape-out… Read More

3D: Atlanta and Burlingame

Two conferences on 3D, one just over and one coming up next week. The one that was just over was hosted by Georgia Tech, the 3rd Annual Global Interposer Technology Workshop (GIT). I wasn’t there but my ex-colleague from VLSI Technology Herb Reiter was. Herb has become very much associated with all things 3D since he led the … Read More

A Brief History of DSP…Not By Any of Us

I came across an interesting article by Will Strauss which is pretty much the history of DSP in communication chips. Having lived through the early part of the history while I was at VLSI Technology I found it especially interesting.

At VSLI, our first GSM (2G, i.e. digital not analog air interface) was a 5-chip chipset. The DSP functionality… Read More

SPICE Development Roadmap 2013!

The MOS-AK/GSA Modeling Working Group, a global compact modeling standardization forum, delivered its annual autumn compact modeling workshop on Sept. 20, 2013 as an integral part of the ESSDERC/ESSCIRC Conference in Bucharest (RO). The event received full sponsorship from leading industrial partners including Agilent… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!