We are writing technical blogs all along the year, sometime it’s good to write about something completely different. Don’t worry, I don’t plan to write any geo-political analysis, neither propose tourism advertising for Cuba. I just wish to share with you the feeling you have when spending a few weeks in Cuba like I did in the mid … Read More

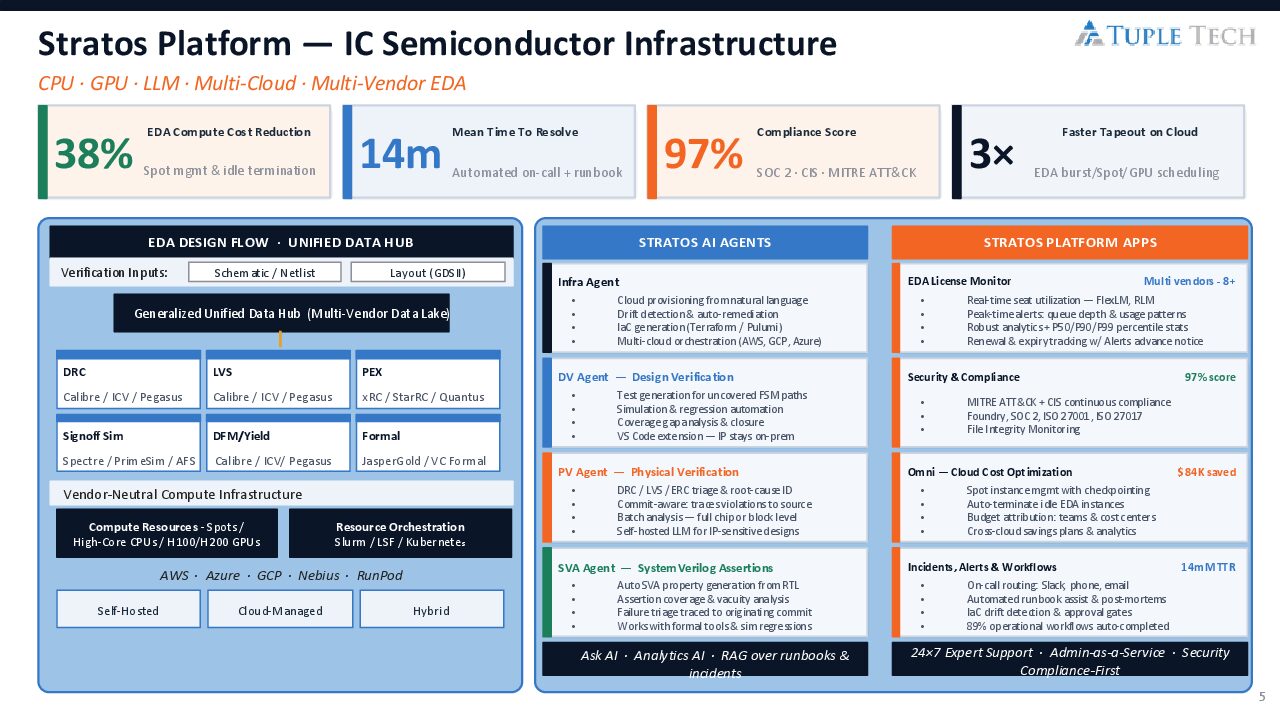

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreExpert Tool to Easily Debug RTL and Reuse in SoCs

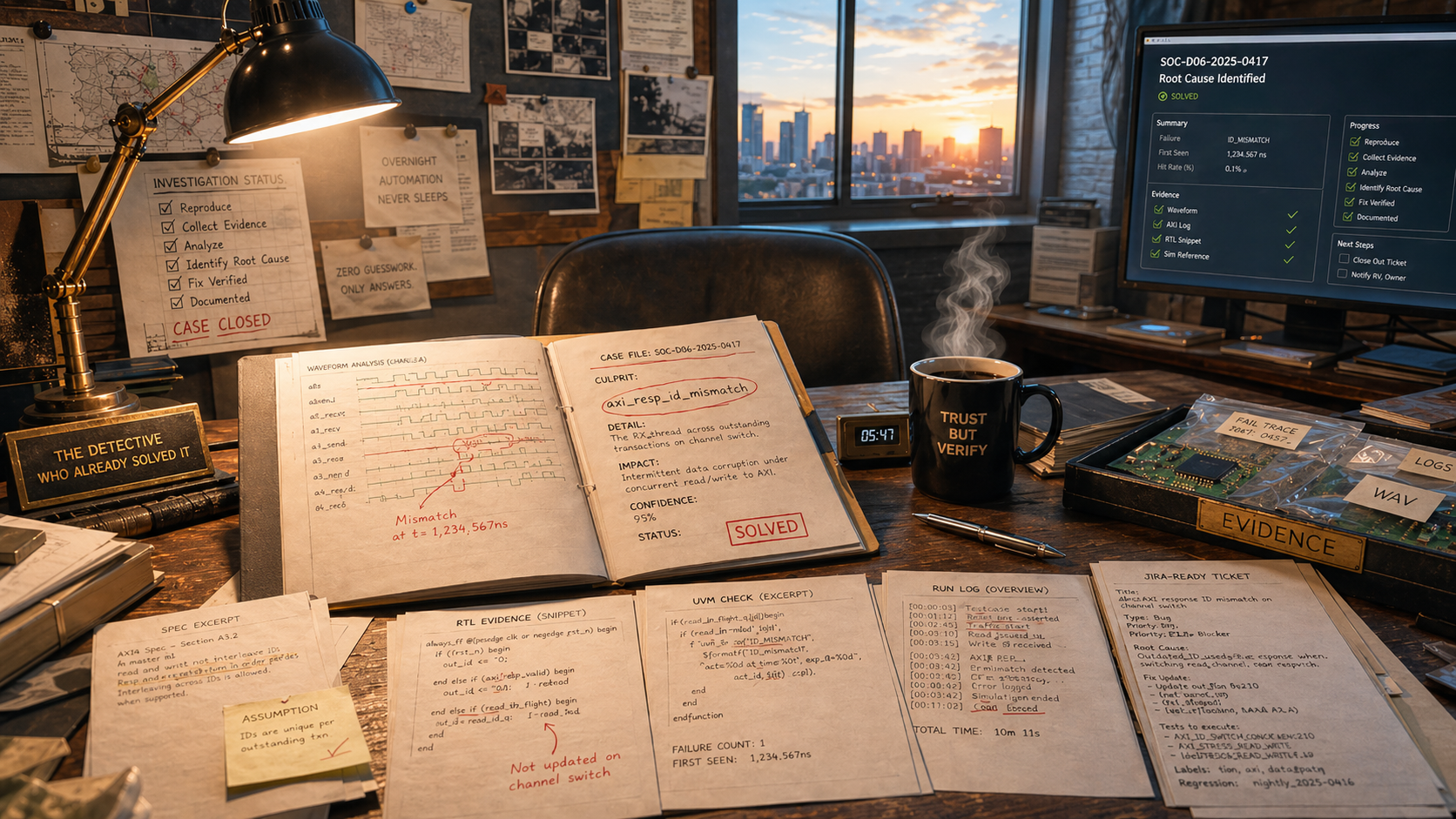

SoC design these days has become a complex and tricky phenomenon involving integration of multiple IPs and legacy RTL code which could be in different languages, sourced from various third parties across the globe. Understanding and reusing RTL code is imperative in SoC integration which needs capable tools that can accommodate… Read More

How are the IoT and ESL Related?

A recent comment by a DACattendee mentioned that the IoT acronym was so over-used as to make him get upset at EDA vendors that all purport to be enabling the growing IoT revolution. One of the most common requirements that I hear about IoT electronics is that the power needs to be well understood and controlled during the design exploration… Read More

IEDM: TSMC, Intel and IBM 14/16nm Processes

This week is IEDM. Three of the presentations today were by TSMC, Intel and IBM going over some of the details of their 14/16nm processes. They don’t provide the slides at IEDM, just the single page papers so this may end up being a somewhat random collection of facts.

TSMC were up first. They talked about the improvements that… Read More

Chinese Apple In Trouble – What to look forward?

Xiaomi, an aspirant to top the Smartphone market through its disruptive entry into the maturing mobile phone market with its high quality Smartphones at rock bottom prices is getting roadblocks in its second largest market, India. It surreptitiously entered into today’s top mobile phone market in its home ground, China and in… Read More

Winning the IoT protocol battle with DSP

There are too many IoT protocols. Way too many. Anyone who says one single protocol will be the winner from end-to-end in all IoT applications and markets is smoking something. Software defined, multi-protocol gateways are the only hope on the IoT – and DSP cores enable this strategy.… Read More

Jean-Louis Gassée on Intel and Mobile

I came across a very interesting article/blog written over the weekend by Jean-Louis Gassée on Intel and mobile. It covers some similar ground to several of my blog posts on the topic but also has some new facts. And it has additional credibility since Jean-Louis was head of product development and worldwide marketing at Apple (pre-iPhone).… Read More

NoC IP boosts SoC reliability, fault tolerance

System-on-chip (SoC) devices are increasingly becoming more complex in terms of adding functionality yet they need to be more reliable and fault tolerant for automotive, aerospace and industrial electronics.

Arteris Inc.—which invented the network-on-chip (NoC) interconnect technology back in 2006—is now offering FlexNoC… Read More

A Closer Look at the QCOM $40M Investment in China!

Last Thursday night was the 20[SUP]th[/SUP] annual GSA Awards Dinner which probably hosts one of the largest collections of semiconductor executives. Think of a movie or music awards show with all of the trimmings including Jay Leno as the keynote. I don’t know the exact head count but there were 160 dinner tables with 10 plates … Read More

Virtual Emulation Extends Debugging Over Physical

Amid burgeoning complexity of SoC verification with ever increasing hardware, software and firmware content, verification engineers are hard pressed with learning multiple tools, technologies and methodologies and still completing SoC verification with full accuracy in time. The complexity, size and diversity of SoC … Read More

Siemens U2U 3D IC Design and Verification Panel