Yes, it is that time of year again, the 2026 TSMC Technology Symposium kick-off event in Silicon Valley. TSMC has never been in a better position to forecast the future of semiconductor technology and the industry itself. TSMC closely collaborates with the top semiconductor companies around the world and the top players in the semiconductor ecosystem. Never in the history of TSMC have they been in such a prominent position and the information that comes from that is astounding.

Dr. Kevin Zhang, Senior Vice President and Deputy Co-COO, again honored us with a press briefing before the event which is what we are talking about today. Next week we will talk in more detail about the event itself and some of the announcements. Unlike most of the media I will be there live with SemiWiki blogger Kalar Rajendiran.

Again, this is TSMC’s perspective on the semiconductor industry but it is backed collectively by the entire semiconductor ecosystem, absolutely.

The semiconductor industry is entering a new phase of accelerated growth and architectural transformation, driven primarily by artificial intelligence (AI) and high-performance computing (HPC). Recent projections indicate that semiconductor market growth has significantly outpaced earlier expectations, rising from a forecasted 10% to an actual 23% annual increase, with future projections reaching approximately 45% growth . This rapid expansion is largely attributed to AI-driven demand, which is reshaping both technology development and system-level design.

Could this be the first year that the semiconductor industry outpaces TSMC? Hard to believe but yes. TSMC revenue is expected by me to grow 30-40%. Here is the hitch: While wafer pricing is stable chip pricing is not. The bulk of the 45% revenue growth is due to chip pricing versus chip unit sales. Memory pricing is a big part of this but some of the AI chips (NVIDIA) are also selling at a premium.

![]()

A major milestone in this transformation is the advancement of global semiconductor revenue toward the $1 trillion mark, now expected to be achieved earlier than previously projected. As illustrated in the industry trend chart, AI represents the latest inflection point following previous computing waves such as PCs, the internet, and smartphones. By 2030, the semiconductor market is expected to exceed $1.5 trillion, with HPC and AI contributing over 55% of total demand, far surpassing other segments like smartphones (20%), automotive (10%), and IoT (10%) .

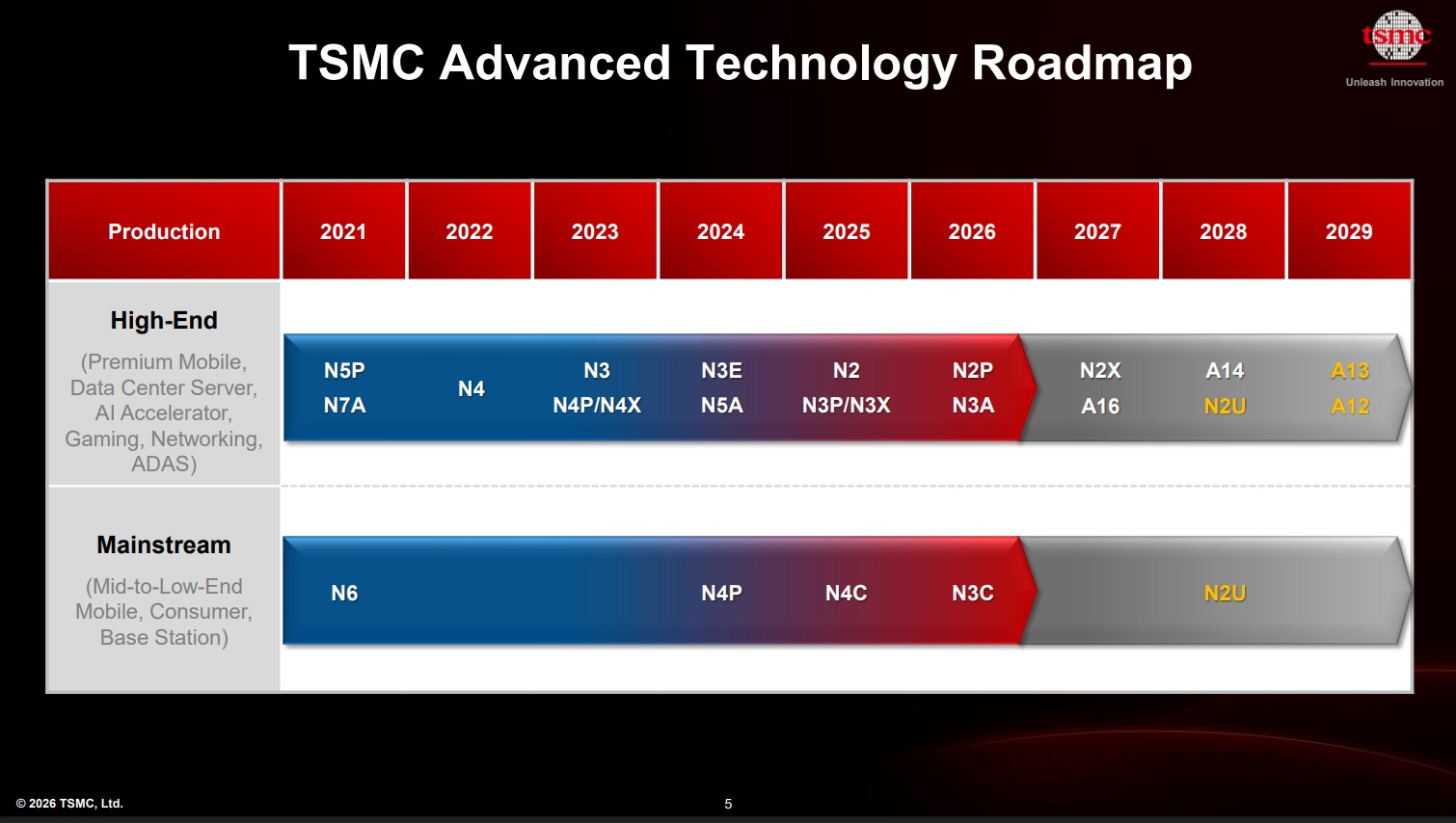

At the core of this growth is continuous innovation in semiconductor process technology. The roadmap for advanced nodes demonstrates a steady progression from nanometer-scale fabrication toward angstrom-class technologies. Nodes such as TSMC N2 and its enhanced derivative TSMC N2U focus on improving power, performance, and area (PPA) through design-technology co-optimization (DTCO). According to the technical data presented, N2U offers a 3–4% speed improvement at constant power, up to 10% power reduction at the same speed, and a modest increase in logic density. These incremental improvements are critical for maximizing return on investment for chip designers while maintaining compatibility with previous node designs.

Further advancements are seen in next-generation nodes such as A13, which extend technology leadership through optical shrink techniques. A 97% optical shrink enables approximately 6% area reduction while preserving backward compatibility in design rules. This allows designers to benefit from improved density without requiring extensive redesign, thereby accelerating product deployment.

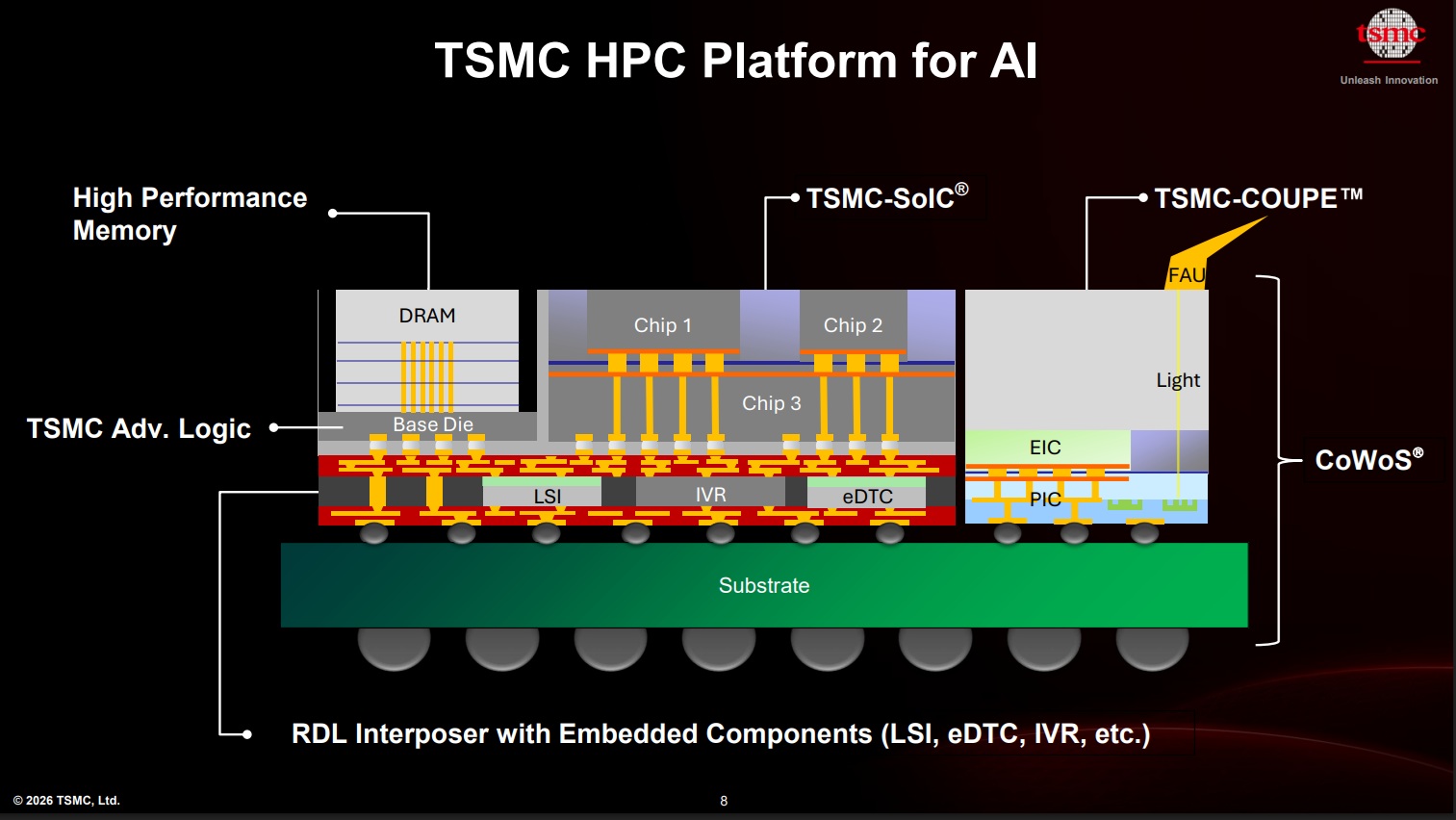

While transistor scaling remains important, it is no longer sufficient to meet the exponential demands of AI workloads. Consequently, advanced packaging and system integration technologies have become central to performance scaling. Technologies such as CoWoS (Chip-on-Wafer-on-Substrate) and SoIC (System-on-Integrated-Chips) enable heterogeneous integration of logic and memory components. The HPC platform diagram illustrates how advanced logic dies, high-bandwidth memory (HBM), and photonic components are integrated into a single package to maximize compute density and efficiency.

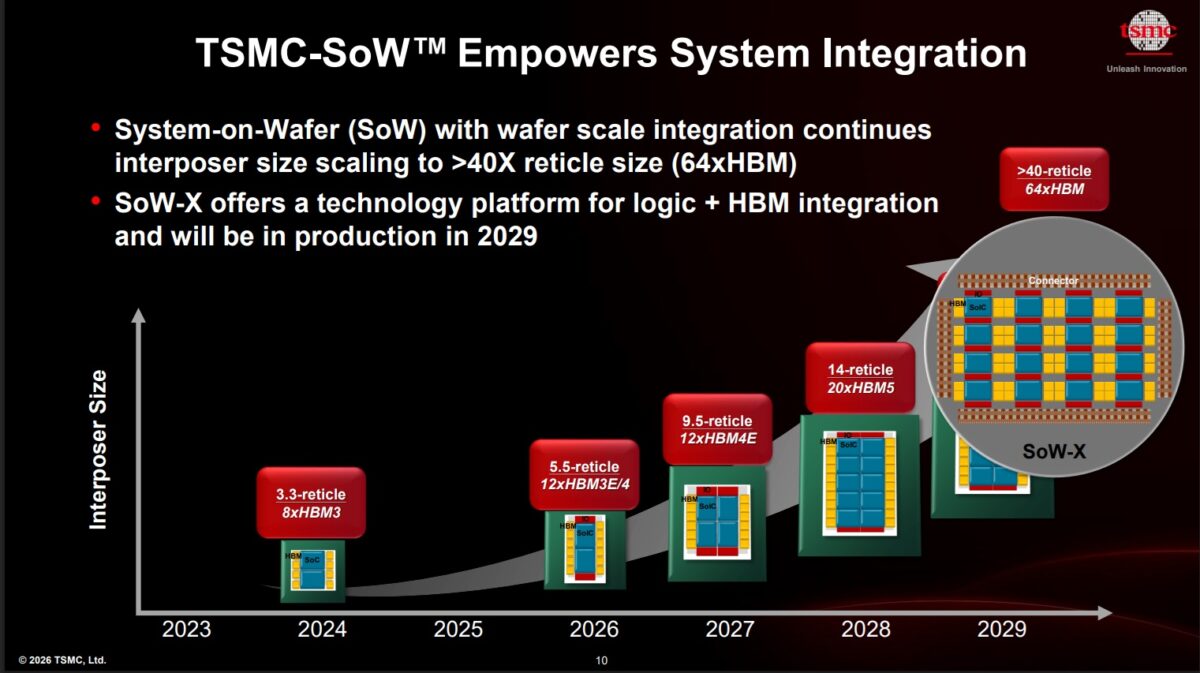

The scaling of interposer size is a key enabler of this integration. Interposer capacity is expanding from 3.3 reticle sizes to over 14 reticles by 2029, supporting up to 24 HBM stacks. This expansion allows for massive increases in memory bandwidth and compute capability. Additionally, wafer-scale integration technologies such as System-on-Wafer (SoW) extend this concept further, enabling integration at scales exceeding 40 reticles, equivalent to 64 HBM stacks.

Three-dimensional stacking technologies also play a critical role in enhancing interconnect density and power efficiency. SoIC technology enables vertical integration with significantly higher interconnect density—up to 56× compared to traditional 2.5D approaches—and improved power efficiency. This shift from planar to vertical integration reflects a broader industry trend toward system-level optimization rather than purely transistor-level scaling.

The impact of these innovations is evident in system-level performance metrics. The number of compute transistors within a single CoWoS package is projected to increase by up to 48× between 2024 and 2029. Similarly, memory bandwidth is expected to scale by 34× during the same period, driven by advancements in HBM technology and integration techniques.

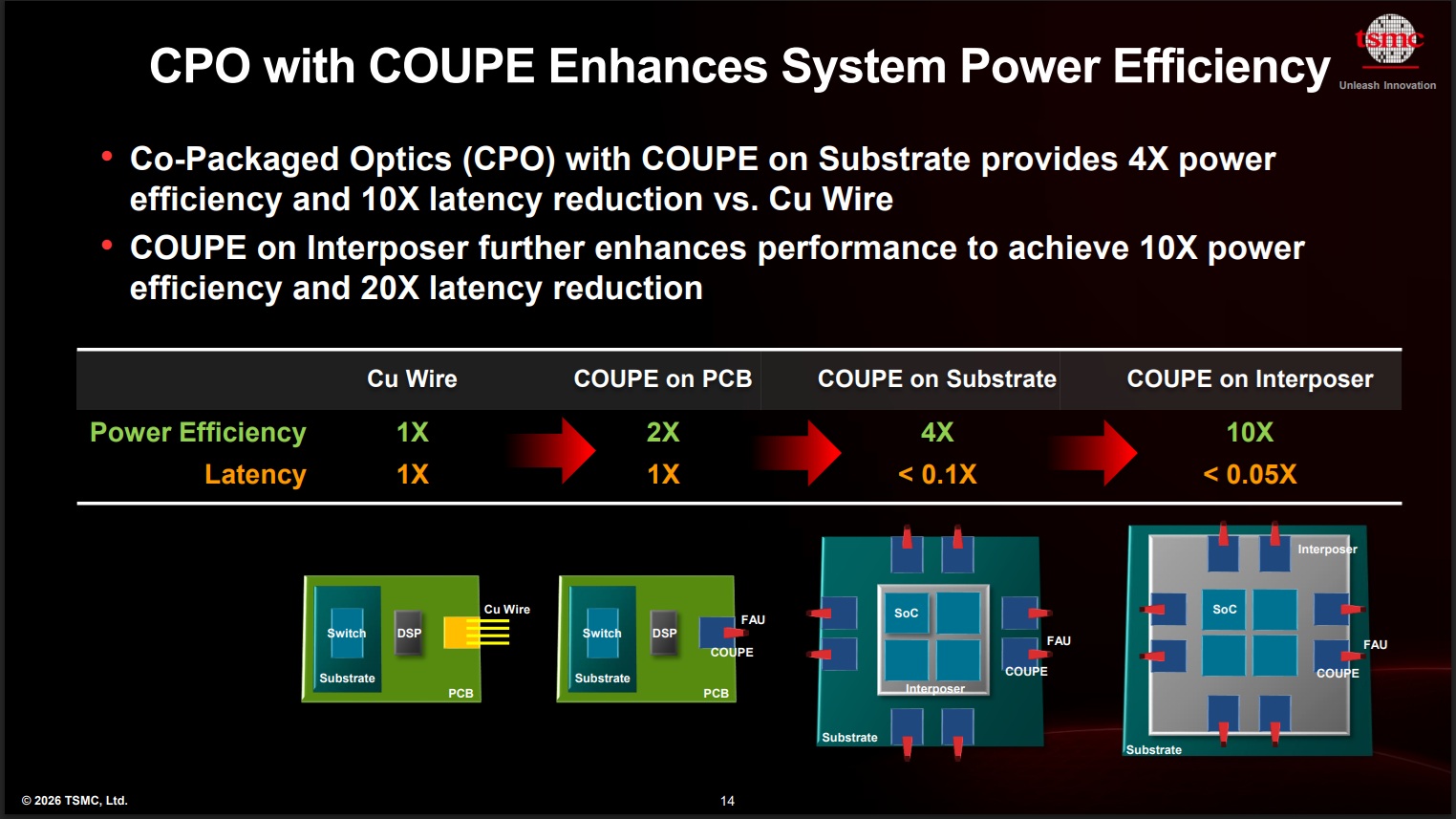

Another critical innovation is the adoption of co-packaged optics (CPO) for high-speed interconnects. Traditional electrical interconnects face limitations in power efficiency and latency. By integrating optical communication directly into the package, systems can achieve up to 10× improvements in power efficiency and 20× reductions in latency, as shown in a performance comparison chart. This transition from electrical to optical signaling is essential for scaling AI infrastructure, where massive data movement between compute units is required.

Beyond data centers, semiconductor advancements are also enabling the emergence of physical AI applications, particularly in automotive and robotics. Modern vehicles are evolving into compute-centric platforms with significantly increased silicon content, incorporating advanced processors, sensors, and connectivity modules. Looking forward, humanoid robots represent a convergence of digital AI and physical interaction, requiring integrated systems for sensing, computation, motion control, and power management.

Bottom line: The semiconductor industry is transitioning from traditional scaling paradigms to a holistic, system-level approach that integrates advanced process nodes, heterogeneous packaging, photonics, and AI-driven architectures. This convergence is enabling unprecedented growth in computational capability and will define the technological landscape of the next decade.

Also Read:

TSMC to Elon Musk: There are no Shortcuts in Building Fabs!

TSMC Technology Symposium 2026: Advancing the Future of Semiconductor Innovation

Global 2nm Supply Crunch: TSMC Leads as Intel 18A, Samsung, and Rapidus Race to Compete

Share this post via:

Comments

2 Replies to “TSMC Technology Symposium 2026 Overview”

You must register or log in to view/post comments.