By Samar Abd El-Hady and Wael ElManhawy

Design teams today face an uncomfortable truth: the specialized tools they need to verify modern ICs can’t reliably share the same design data. As geometries shrink below five nanometers and designs incorporate billions of transistors across multiple dies, no single Electronic Design Automation (EDA) tool can address every verification, analysis and modeling challenge.

Design teams routinely use specialized tools for parasitic extraction, power integrity analysis, electromagnetic simulation and soft error rate prediction. Each tool excels in its domain, but this creates a fundamental problem: how do you make sure that all these tools work from the same verified design data without manual translation, reformatting or error-prone data transfers?

This interoperability crisis demands a solution that can bridge the gap between verification and analysis tools. The Calibre Connectivity Interface (CCI) does this by transforming Layout vs. Schematic (LVS) verification data into a universal data source that downstream tools can query with precision and confidence.

Mining the SVDB: How CCI extracts verified design data

At its core, CCI operates on the Standard Verification Database (SVDB) generated during a Calibre nmLVS verification run. This database contains far more than simple pass or fail verification results. The SVDB captures the complete connectivity graph of the design, including layout geometry coordinates, net topology, device parameters, hierarchical relationships and the critical mapping between layout elements and their corresponding schematic or source names.

CCI provides a structured query interface to this rich dataset. Through the Query Server Tcl shell and Calibre YieldServer implementations, downstream tools can extract precisely the information they need. A typical CCI workflow begins with a completed LVS run that generates the SVDB. The CCI command file then specifies what data to extract and in what format. The interface processes these commands against the SVDB and outputs files tailored to the requirements of specific third-party tools.

Figure 1 illustrates this flow, showing how layout, source and rules feed into Calibre nmLVS, which generates the SVDB. CCI then acts as the bridge between this verified database and the diverse ecosystem of analysis tools.

Feeding parasitic extraction tools with accurate connectivity data

Third-party parasitic extraction tools represent one of the most demanding integration scenarios. These tools need comprehensive access to geometric layouts, detailed connectivity information, net and instance names, device characteristics and port definitions. The accuracy of parasitic RC models depends entirely on the fidelity of this input data.

CCI is specifically engineered to provide all this essential data through flexible application programming interfaces (APIs). Each parasitic extraction tool can precisely query and retrieve the specific data it needs. Here’s how different tools leverage CCI:

Empyrean’s PEX tool uses CCI data to generate layout analysis with parasitic RC extraction and critical path netlists with RC annotation.

Phlexing’s GloryEX extraction tool leverages CCI to support advanced 3D modeling for planar gate, FinFET, gate-all-around and other complex device structures. GloryEX also handles sophisticated process modeling including chemical mechanical planarization, etch effects and multi-patterning, while providing high-speed capacitance table generation and pattern matching for 2.5D flows at both gate and transistor levels.

Synopsys StarRC and Cadence QRC demonstrate CCI’s ability to interface with industry-standard sign-off tools. Both tools benefit from dedicated APIs that provide real-time access to device-level layout data, robust SPICE model correlation, geometry-to-schematic mapping, automated net hierarchy tracing and seamless integration into full-chip sign-off flows.

Correlating electromagnetic analysis for high-frequency designs

For high-speed designs operating at multi-gigahertz frequencies, electromagnetic effects in critical signal paths can determine whether a design meets timing and signal integrity requirements. Siemens collaborated with Lorentz Solution, Inc. to integrate Calibre nmLVS with Lorentz PeakView products using CCI.

Together, the tools create a high-frequency design flow that delivers ease of use while enabling IC and 3D IC designers to develop post-layout solutions correlated with source and schematic names, devices and hierarchy. This correlation throughout the electromagnetic analysis workflow means you can trace results back to specific design elements for debugging and optimization.

Streamlining power integrity analysis with comprehensive grid data

Power delivery network analysis has become critical as voltage margins shrink and current densities increase. CCI integrates with mPower, the Siemens power integrity solution that provides comprehensive analysis for digital, analog and complex 3D IC architectures across all design flows.

This integration enables high-resolution voltage drop (IR) and electromigration (EM) analysis, full-chip power grid modeling and accurate power pin annotation with connectivity tracing. The key enabler is CCI’s ability to seamlessly provide all essential input data to the mPower flow—Annotated Geometry Files (AGF), detailed device data and cross-reference files. Figure 2 illustrates how CCI feeds this critical data into the mPower design import flow, ensuring accurate and efficient execution of power integrity analyses.

Automating soft error analysis for radiation-hardened designs

Many semiconductor devices operate in harsh environments, from automotive applications to aerospace systems, making soft error analysis essential. CCI successfully interfaces with IROC Technologies, a leader in enhancing electronic system reliability through specialized EDA solutions.

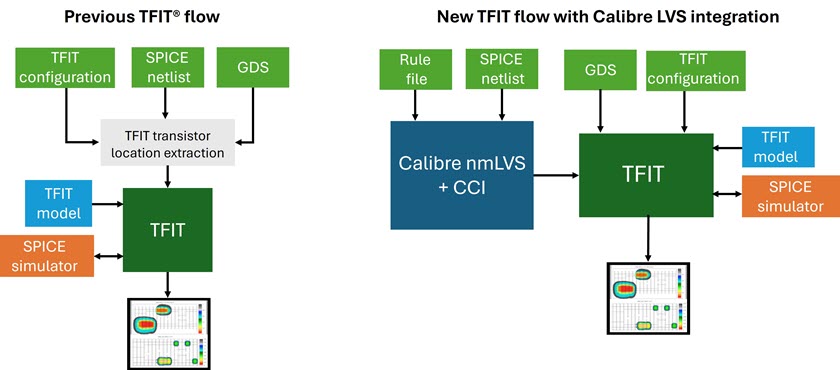

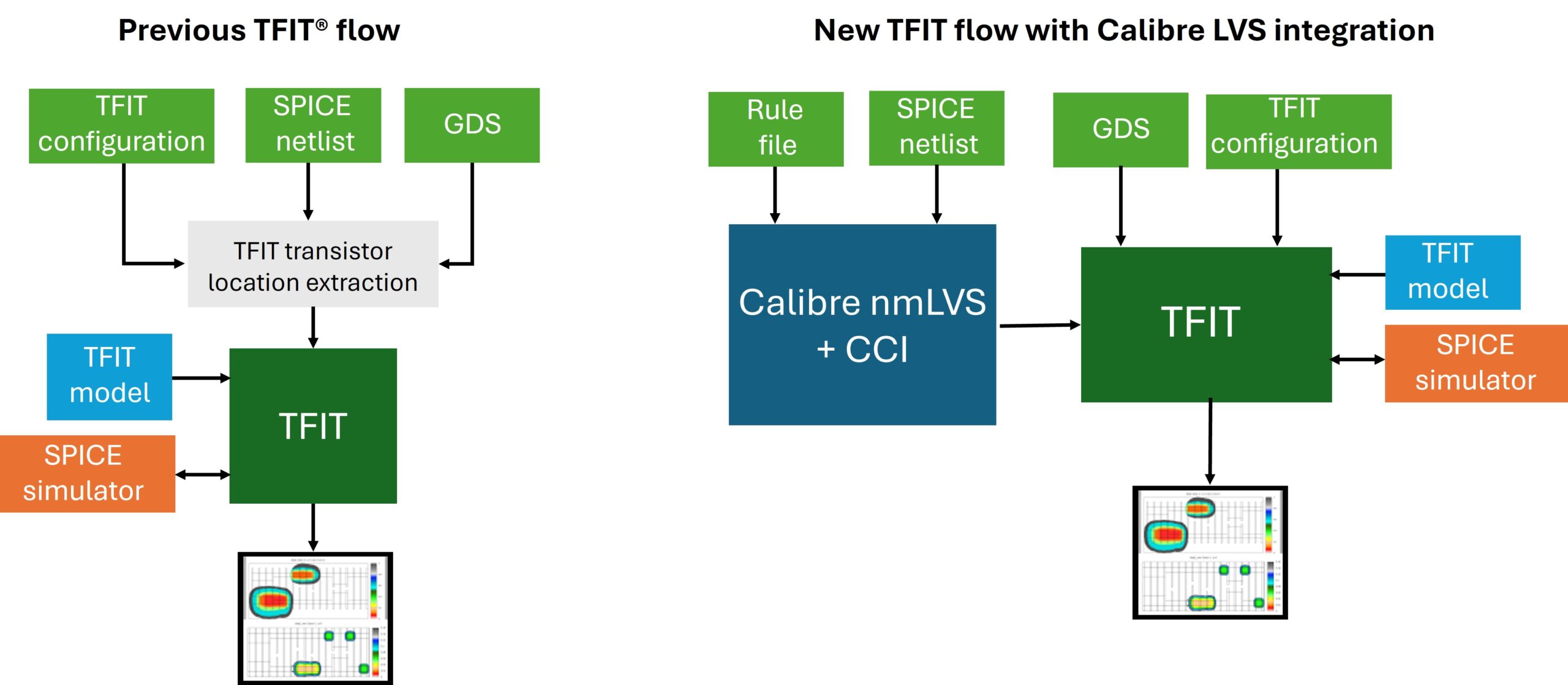

IROC’s cell-level soft error detector, TFIT (Transistor Failure in Time), needs precise transistor drain and source diffusion coordinates from GDS files to perform its analysis. The output consists of detailed sensitivity maps identifying vulnerable zones within the design. Before integrating with CCI, IROC relied on a custom LVS module with limited technology support and error-prone workflows.

By integrating with Calibre nmLVS through CCI, a new reliable and automated flow emerged. Figure 3 compares the previous TFIT design import flow with the new automated flow using Calibre nmLVS and CCI. The new flow extracts accurate drain and source locations, executes the TFIT flow with precise input data, eliminates previous technical limitations and streamlines the entire analysis process.

Deploying CCI across multi-tool verification workflows

To understand the practical value of CCI, consider these real-world applications across multi-tool workflows: In automotive IC sign-off, design teams combine parasitic extraction using StarRC with soft error rate analysis using TFIT. CCI makes sure both tools get consistent, verified design data so you can count on functional correctness and reliability over extended temperature and voltage ranges.

For 2.5D and 3D IC integration, a single design stack benefits from CCI feeding both mPower and GloryEX simultaneously. This lets you run comprehensive interposer parasitic analysis and package power analysis from a common verified database, eliminating potential inconsistencies from using different data sources.

Analog and mixed-signal designers leverage CCI for electromagnetic validation, parasitic-aware simulation and noise coupling prediction with various third-party tools. The ability to maintain correlation between layout and schematic throughout these analyses proves crucial for sensitive analog circuits where small parasitic differences can affect performance.

Building a foundation for seamless multi-tool integration

In today’s complex IC design landscape, seamless collaboration between EDA tools has evolved from a convenience to an absolute necessity. The Calibre Connectivity Interface serves as a critical integration hub, enabling efficient data exchange and communication across diverse design and verification workflows.

By transforming LVS verification data from a simple pass or fail check into a comprehensive, queryable design database, CCI provides a robust foundation for the specialized tool ecosystem that modern IC design requires. As design complexity continues to increase and new analysis requirements emerge, this foundational integration technology proves indispensable for enhancing design accuracy, streamlining verification cycles and accelerating time-to-market for cutting-edge semiconductor innovation.

Samar Abd El-Hady is a Advanced Product Engineer, Calibre Design to Silicon Division, at Siemens EDA, a part of Siemens Digital Industries Software. She is supporting Calibre LVS, layers promotion, CCI, V2LVS and ML activities . Samar has been working in Siemens EDA for over 6 years. Before, she received her BS in electronics & communication engineering in 2019 from Ain Shams University in Cairo, Egypt. After graduation, Samar joined Siemens EDA as a PE supporting Calibre LVS.

Wael ElManhawy is a Director in Calibre Management at Siemens EDA, responsible for leading the Calibre LVS product line. He brings 29 years of experience in VLSI and EDA, specializing in physical and circuit verification, including 26 years at Siemens EDA and 21 years working on Calibre, where he has played a key role in shaping different Calibre products strategy, technology, and customer adoption at the most advanced nodes.

Also Read:

Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White Paper

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design Enablement

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB Design

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.