By Samar Abd El-Hady and Wael ElManhawy

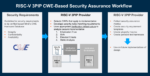

Design teams today face an uncomfortable truth: the specialized tools they need to verify modern ICs can’t reliably share the same design data. As geometries shrink below five nanometers and designs incorporate billions of transistors across multiple dies, no single Electronic… Read More

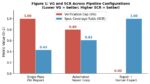

Solving the EDA tool fragmentation crisis