At the recent RISC-V Now event hosted by Andes, the discussion underscored the fact that RISC-V is no longer just about instruction set architecture advantages or customizable cores. The real focus has moved up the stack to system-level design. This is where connectivity, integration, and security define whether an innovation can scale.

This shift reflects a broader reality: modern SoCs are no longer simple, monolithic designs. They are complex, heterogeneous systems that must seamlessly integrate multiple compute domains, memory hierarchies, and specialized accelerators. In this environment, the success of RISC-V depends not only on openness, but on how effectively that openness can be orchestrated into a cohesive and efficient system.

Guillaume Boillet, Vice President of Strategic Marketing at Arteris framed his talk around a central thesis: that RISC-V’s long-term success will hinge not just on open architectures, but on mastering integration, embedding security at the hardware level, adopting true systems thinking, and leveraging deep ecosystem collaboration.

The Hidden Bottleneck: Data Movement and System Complexity

One of the most compelling insights from the presentation is that compute is no longer the dominant constraint in system performance. Instead, data movement has emerged as the primary bottleneck. A significant portion of system energy is consumed simply moving and storing data, especially in GPU-class SoCs

This has profound implications. As workloads like artificial intelligence (AI) and real-time analytics continue to grow, the efficiency of the interconnect fabric becomes just as important as the performance of the compute engines themselves. The architecture must be designed to minimize latency, optimize bandwidth, and reduce power consumption associated with moving data across increasingly complex systems.

At the same time, the rise of chiplets and multi-die architectures introduces new layers of design complexity. What was once contained within a single piece of silicon must now operate across multiple interconnected dies, each potentially optimized for different functions. This transforms connectivity from a supporting role into a central architectural pillar.

RISC-V’s Promise Meets Integration Reality

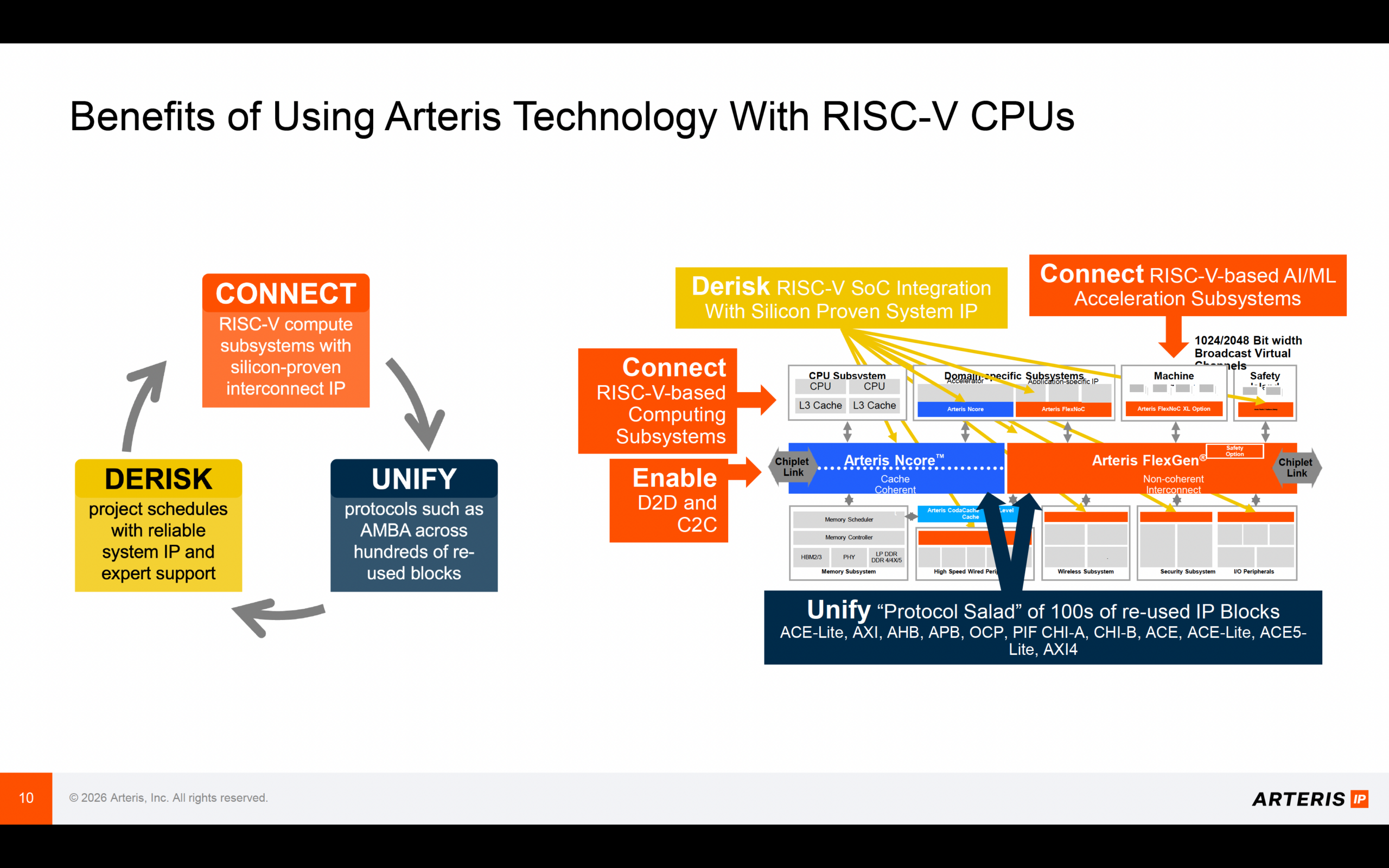

RISC-V’s flexibility is one of its greatest strengths, but it also introduces a unique challenge: integration. The ability to mix and match IP from different sources creates enormous opportunity, yet it also leads to fragmentation if not managed carefully.

Modern SoCs often incorporate a wide array of IP blocks, each using different communication protocols. Bringing these together into a unified system requires a robust and adaptable interconnect strategy. Without it, the very modularity that makes RISC-V attractive can become a source of inefficiency and risk.

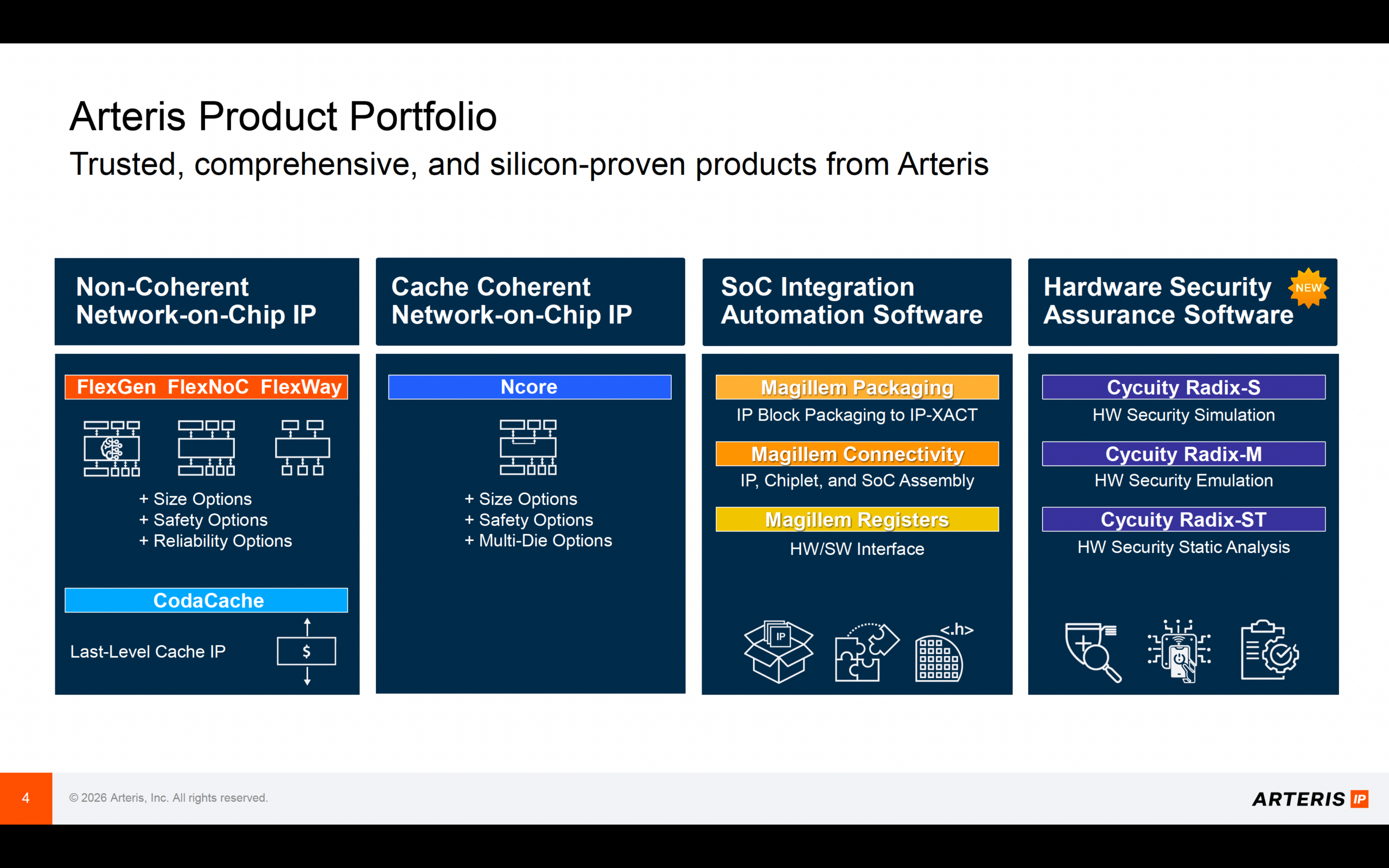

This is where Network-on-Chip (NoC) technologies play a crucial role. By providing a scalable and configurable communication backbone, they enable designers to integrate diverse components while maintaining performance and efficiency. The interconnect effectively becomes the glue that holds the system together, ensuring that all parts can communicate reliably despite their differences.

Automotive and AI: Stress Testing the Architecture

The growing demands of automotive and AI applications highlight just how critical system-level design has become. In automotive systems, especially those supporting advanced driver assistance and autonomous capabilities, architectures must handle a mix of workloads with different safety and performance requirements. Some functions demand strict determinism and compliance with safety standards, while others require high-throughput data processing.

These systems are also evolving toward chiplet-based implementations, further increasing the importance of reliable and scalable interconnects . The ability to manage both coherent and non-coherent data flows across such architectures is essential for ensuring system integrity and performance.

AI workloads present a different but equally demanding challenge. As AI becomes more pervasive, the need for specialized accelerators continues to grow. Integrating these accelerators efficiently into the broader system requires careful orchestration of data movement and memory access. Without a well-designed interconnect, the benefits of these accelerators can be significantly diminished.

The Overlooked Risk: Hardware Security

Another critical theme is the increasing importance of hardware security. Historically, security efforts have focused on software and network layers, but recent vulnerabilities have demonstrated that hardware itself can be a significant point of exposure.

The number of reported hardware vulnerabilities has been rising, reflecting a growing awareness of this issue . As systems become more complex and interconnected, the potential attack surface expands, making it essential to address security at the hardware level from the outset.

This requires new approaches to design and verification, including the ability to identify and mitigate vulnerabilities early in the development process. Hardware security is a foundational requirement for modern SoCs, not an afterthought.

Ecosystem Collaboration as a Force Multiplier

The collaboration between Andes and Arteris illustrates the importance of ecosystem-level solutions in addressing these challenges. By pre-validating the interoperability between processor cores and interconnect technologies, they reduce integration risk and accelerate development timelines.

![]()

This kind of partnership reflects a broader trend in the industry toward platform-based design. Instead of building systems from scratch, companies are increasingly relying on pre-validated components that can be assembled into complete solutions. This approach not only improves efficiency but also increases confidence in achieving first-pass silicon success.

From Components to Systems Thinking

The overarching message: the industry must move from a component-centric mindset to a system-centric one. Designing a successful RISC-V-based SoC today requires a holistic understanding of how all parts of the system interact.

It is no longer sufficient to optimize individual components in isolation. Designers must consider how data flows across the system, how different subsystems communicate, and how security is enforced at every level. This shift in perspective is essential for managing the complexity of modern designs.

Summary

RISC-V is well positioned to thrive in this new environment, but its success will depend on more than just its open architecture. It will require robust solutions for connectivity, integration, and security as these aspects are becoming increasingly critical as systems grow in complexity.

The future of RISC-V will be defined not just by its flexibility, but by its ability to deliver complete, scalable, and secure systems. Those who embrace this systems-level approach will be best equipped to lead the next wave of semiconductor innovation.

To learn more, visit Arteris.com

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.