When I first started working in the semiconductor industry back in 1982, I realized that there was a race going on between the complexity of the system being designed and the capabilities of the technology in the tools and systems used to design them. The technology used to design the next generation of hardware was always lagging… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read MoreCadence in the Cloud!

The first clue was cloud vendors (Amazon, Google, IBM, etc…) at 55DAC for the first time ever with lots of cloud content including a Design on Cloud Pavilion. The second clue was the pre-briefing from Cadence last week. There has also been a lot of cloud chatter in the semiconductor ecosystem so yes, I saw this coming and EDA will get… Read More

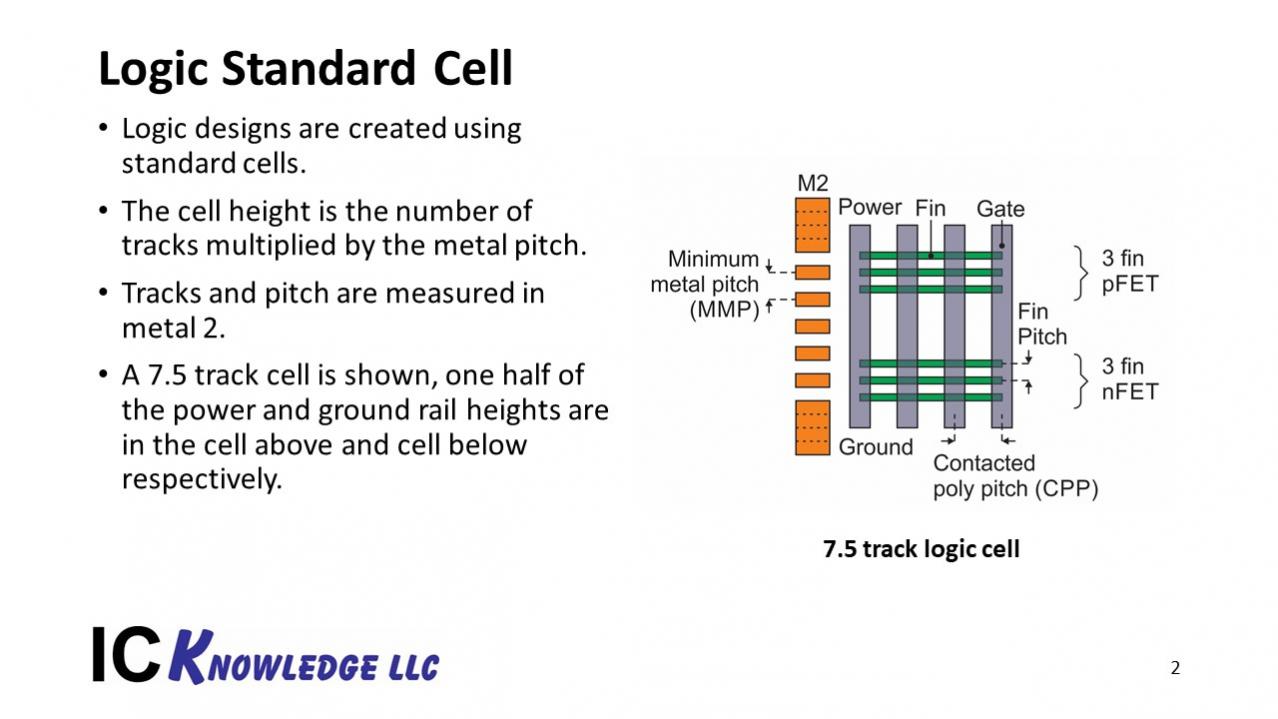

7nm, 5nm and 3nm Logic, current and projected processes

There has been a lot of new information available about the leading-edge logic processes lately. Papers from IEDM in December 2017, VLSIT this month, the TSMC and Samsung Foundry forums, etc. have all filled in a lot of information. In this article I will summarize what is currently known.… Read More

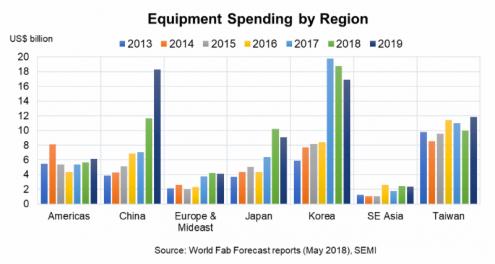

Semiconductor Cycles Always End the Same Way

It appears the current cycle has rolled over? The reason is memory & could be worsened by trade Figuring out length, depth and impact of the downturn? We had said that AMAT “called” the top of the cycle on their last conference call even though they may not think so. Semiconductor cycles always ends the same way. The… Read More

Mentor at the 55th Design Automation Conference

It’s hard to believe that this is the 55th DAC and even harder to believe that this will be my 35th. So much has changed in 35 years, with DAC back in San Francisco I expect a VERY big crowd and even bigger announcements, absolutely.

Not only is this an epic time for semiconductors, I would say that EDA is exciting again and the Mentor… Read More

Folklore Around the HP 35 LED Development and the Nobel Prize

This is the third in the series of “20 Questions with Wally Rhines”

In the early 1970s I was working on a PhD thesis based upon GaAs light emitting diodes, or LEDs. Many of my predecessors in the Materials Science and Engineering Department at Stanford had worked on other aspects of III-V compounds and some of them went… Read More

Achieving Clean Design Early with Calibre-RTD

Functional and physical verification are easily the two long poles in most IC product developments. During a design implementation cycle, design teams tend to push physical verification (PV) step towards the end as it is a time consuming process and requires significant manual interventions.

PV Challenges

In the traditional… Read More

What to Expect from Methodics at DAC

I’ve been visiting DAC for decades now, at first as an EDA vendor and since 2004 as a freelance EDA consultant. There’s always a buzz about what’s new, semiconductor industry trends, who is getting acquired and the latest commercial EDA and IP offerings. There’s so much vying for my attention at DAC each… Read More

ANSYS at DAC

I’m not going to be at DAC this year because I scheduled a fishing trip at the end of June, assuming the show would stay true to form as an early/mid-June event. Still, having to endure salmon and halibut fishing in Alaska rather than slogging around Moscone Center, I can’t pretend to be too disappointed; I’ll be thinking of you all 😎.… Read More

HOT Party for a Cause at DAC 55

The Design Automation Conference (DAC), now in its 55[SUP]th[/SUP] year, always offers a lively mix of activities. For EDA vendors and their customers, the focus is on the exhibit floor and in booth suites where the latest technology is on display. For R&D engineers and academics, the technical sessions dig deeply into an … Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!