As I wrote last week there is a whole list of companies on LinkedIn with people working on TSMC 16nm. Today TSMC released a list of customers that have risk production 16FF+ silicon. Most of us knew this already but now we can talk about it in more detail. This is a really big deal for the FinFET doubters out there. Just because Intel had… Read More

Let the FinFET Yield Controversy Begin!

It never ceases to amaze me how people point fingers and create controversy to cover their mistakes. It happened at 40nm, 28nm, and again at 20nm and now it is time for the regularly scheduled yield controversy. Of course any conversation about semiconductor yield generates clicks for SemiWiki so I’m happy to play along.

It generally… Read More

Noise & Reliability of FinFET Designs – Success Stories!

I think by now there has been good level of discussion on FinFET technology at sub-20 nm process nodes and this is an answer to ultra dense, high performance, low power, and billion+ gate SoC designs within the same area. However, it comes with some of the key challenges with respect to power, noise and reliability of the design. A FinFET… Read More

ANSYS Tools Shine at FinFET Nodes!

In the modern semiconductor ecosystem we are seeing rapid advancement in technology breaking past once perceived limits; 28nm, 20nm, 16-14nm, 10nm and we are foreseeing 7nm now. Double and multi-patterning are already being seen along with complex FinFET structures in transistors to gain the ultimate advantages in PPA from… Read More

Place & Route with FinFETs and Double Patterning

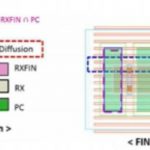

Place & route in the 16/14nm era requires a new approach since it is significantly more complex. Of course, every process generation is more complex than the one before and the designs are bigger. But modern processes have new problems. The two biggest changes are FinFETs and double patterning.

FinFETs, as I assume you know,… Read More

Samsung 14nm FinFET Design with Cadence Tools

The first consumer products with 20nm processing are arriving in 2014 like the 2 billion transistor A8 chip in the iPhone 6, however at the 14nm node there are new designs underway to continue the trend of Moore’s Law. To get a better feel for the challenges of designing with 14nm FinFET technology I watched a 23 minute video … Read More

FinFET Design for Power, Noise and Reliability

IC designers have been running analysis tools for power, noise and reliability for many years now, so what is new when you start using FinFET transistors instead of planar transistors? Calvin Chow from ANSYS (Apache Design) presented on this topic earlier in the summer through a 33 minutewebinar that has been archived. There is… Read More

FinFETs for your Next SoC

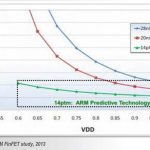

Planar CMOS processes have been offered for decades now, and all the way down through the 28nm node it has been riding the benefits of Moore’s Law. A few years back we started hearing from Intel about TriGate (aka FinFET) starting at the 22nm node as a way to use a more 3D processing approach for transistors instead of planar CMOS.… Read More

What Comes After FinFET?

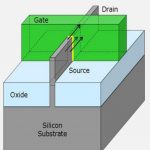

So what comes after FinFETs? At 14/16nm (or 22nm if you are Intel) we had FinFET transistors, where the channel was no longer planar but stuck out of the wafer vertically, and the gate wrapped around it on 3 sides. The key thing that made FinFET transistors attractive was that the channel was thin so that the gate controlled it well. … Read More

Altera vs Xilinx FinFET Update

One of the things I do in my spare time is listen to quarterly conference calls and try to sort fact from fiction. I compare past calls to the current one and attempt to predict what’s coming next. Confucius said, “Study the past if you would define the future” and I’m a big believer in that.

Paul McLellan wrote about the Xilinx call earlier… Read More

Is Intel About to Take Flight?