You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4439

[filter] => raw

[cat_ID] => 157

[category_count] => 4439

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

I recently talked to Trent McConaghy about his book on variation-aware design of custom ICs and the #50DAC tutorial we are doing:

Winning in Monte Carlo: Managing Simulations Under Variability and Reliability.

Trent is the Solido Chief Technology Officer, an engaging speaker, one of the brightest minds in EDA, and someone who… Read More

As Julius Caesar said, “Gallia est omnis divisa in partes tres.” All Gaul is divided into 3 parts. Calypto is similar with three product lines that work together to provide a system level approach to SoC design. Two of those product lines are not unique, in the sense that similar capabilities are available from a handful… Read More

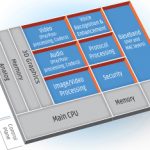

Most SoCs today are being prototyped in FPGA hardware before committing to costly IC fabrication. You could just design and build your own FPGA prototyping system, or instead choose something off the shelf and then concentrate on your core competence of SoC design.

Thanks to the FPGA vendors like Xilinx we now have FGPA prototyping… Read More

The tremendous growth in IC and SoC design complexity has now enabled engineers to place bilions of transistors on a single chip. To make that growth possible design teams resort to using libraries and semi IP provided by other groups in their company, or outside IP vendors. To lower risk, you must know that the IP being used in your… Read More

Sean Dart’s first DAC (Las Vegas) was as a customer in 1989. Designs were hitting 15,000 gates back then so he was looking for better schematic editors and simulators for gate level design. Fast forward 25 years and Sean’s customers are doing 15,000,000 gate subsystems and that number is growing steadily every year.… Read More

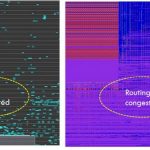

As an applications engineer for over 15 years supporting physical design tools that enable implementation closure, I have seen the complexity of timing closure grow continuously from one process node to the next. At 28nm, the number of scenarios for timing sign-off has increased to the extent that is way beyond the number that … Read More

Design IP, at least Interface IP, is about 15 years old, but the market was made of one large provider – Synopsys- with many small vendors around. Chip makers were not very comfortable with this picture, especially the Tier 1 considering that the risk (to see the big one being acquired by one of their direct competitor, say Samsung… Read More

With nearly twenty five years in business, Tanner EDA Application Engineers have seen a wide range of support requests. One consistent topic area is around design data management and design reuse. In one recent instance, our customer, an IDM who produces imaging sensors for infrared vision systems, called on Tanners AE team for… Read More

Every process node these days has a new “gotcha” that designers need to be aware of. In some ways this has always been the case but the changes used to be gradual. But now each process node has something discontinuously different. At 20nm the big change is double patterning. At 14/16nm it is FinFET.

Rahul Deokar and John… Read More

OK, enough with all this semiconductor geeky stuff. The important thing about DAC is…where to go to eat to avoid standard issue convention center chicken Caesar salad.

And a 7 minute walk from the convention center is Bangers Sausage House and Beer Gardenwhere you can have the $8 “executive” lunch consisting… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era