You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4462

[filter] => raw

[cat_ID] => 157

[category_count] => 4462

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Cadence is a DAC anchor, everyone will visit their booth, so lets look at their technical sessions and put our agendas together. Lets start with the breakfast/lunch sessions because Cadence usually puts out quite a spread, we all gotta eat and free food tastes even better:

Has “Timing Signoff Innovation” Become an Oxymoron? What… Read More

Carbon Design drives a lot of traffic to SemiWiki. Actually, it’s ARM driving traffic to the Carbon landing page since Carbon and ARM work closely together. When we blog about designing with ARM IP droves of people click over. Seriously, DROVES of people. Rick Lucier has deep EDA experience and has led Carbon as CEO for the … Read More

Methodics is new to SemiWiki and I have to tell you I’m really enjoying working with them. Their office is in a great location and the inovation spirit runs strong. Simon Butler is an interesting guy. He first started in EDA with HLD (acquired by Cadence) and was a founder at Sabio Labs (acquired by Magma). In between those startups… Read More

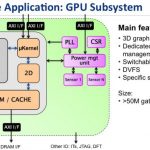

I love it when my Acura goes months and months without any major repair issue or computer-related glitches. Cars or networks only become reliable when they are designed and built for reliability. Freescale designs SoCs for advanced automotive and networking applications, and their engineers know much about the topics of power,… Read More

Cornelia Golovanovworks at LSI Corp in Pennsylvania and is an EMI expert that provides EDA tool and methodology advise to design groups. She earned a PhD in microelectronics and radioelectricity from the Institut national polytechnique de Grenoble, and joined Lucent out of school 12 years ago. We had a chance to talk by phone about… Read More

Today, Jasper announced their new Jasper-Gold Low Power Verification App. This is focused on verifying low power designs with multiple power domains, voltage islands, power shutoff, clock shutoff, and all the other techniques used for reducing power. Of course power is the main driver of SoC design these days, whether it is for… Read More

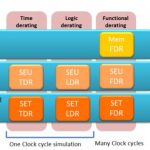

I blogged recently about reliability testing with high energy neutron beams. This is good for getting basic reliability data but it is not really a useful tool for worrying about reliability while the chip is still being designed and something can be done about it.

That is where IROC Technologies SOCFIT tool comes in. It takes all… Read More

At DAC in just three weeks you can learn about which EDA vendors are supporting the latest UVM 1.1d (Universal Verification Methodology) standard as defined by Accellera. One of those EDA vendors is Aldec, and they have a 45 minute technical session that you can register for online. Space will fill up quickly, so get signed up sooner… Read More

A random walk down OS-VVMby Don Dingee on 05-13-2013 at 11:14 amCategories: Aldec, EDA

Unlike one prevailing theory of financial markets, digital designs definitely don’t function or evolve randomly. But many engineers have bought into the theory that designs can be completely tested randomly. Certainly there is value to randomness, exercising all combinations of inputs, including unexpected ones a designer… Read More

Tektronix at #50DACby Daniel Nenni on 05-13-2013 at 10:00 amCategories: EDA

If we grew up in similar eras you will know Tektronix as a company that manufactures test and measurement devices. Every lab I was in during high school and college had Tek oscilloscopes and logic analyzers. At #50DAC however, attendees that visit Tektronix will experience firsthand RTL simulation-level visibility to multi-FPGA… Read More

Solving the EDA tool fragmentation crisis