Today Oasys announced the availability of Floorplan Compiler in the Oasys RealTime suite of physical RTL exploration and synthesis tools. This is actually a repackaging of a capability that has always been in RealTime Designer, and in fact has been an important aspect of how well RealTime Designer has performed in benchmarks over the last four years. Until now, though, it has not been available as a separate tool.

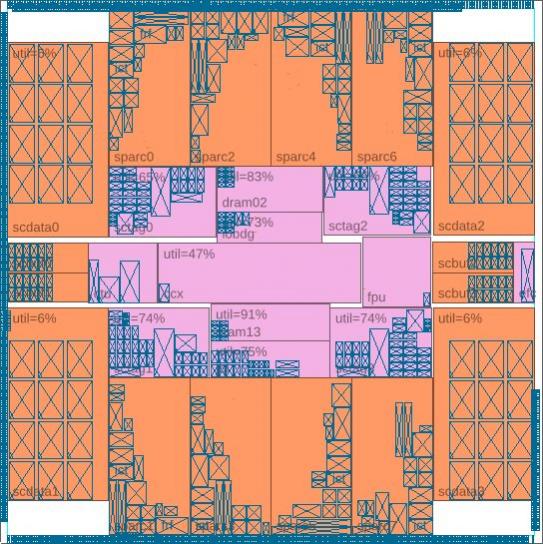

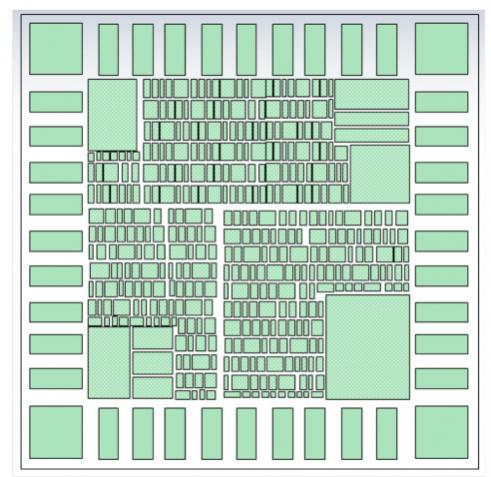

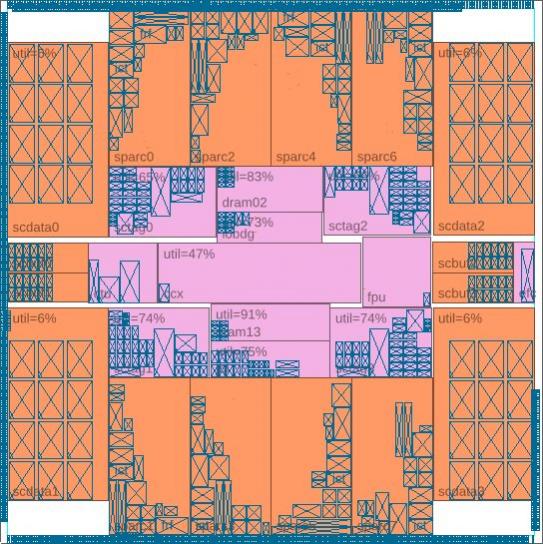

However, now the design team can create a floorplan directly from the RTL that is aware of the design’s dataflow and also meets all the constraints for timing, power, area and routing congestion. The resulting floorplan can then be fed forward as initial guidance to the physical design teams.

However, now the design team can create a floorplan directly from the RTL that is aware of the design’s dataflow and also meets all the constraints for timing, power, area and routing congestion. The resulting floorplan can then be fed forward as initial guidance to the physical design teams.

Floorplan Compiler takes into account regions, fences, blockages and other physical guidance. The advanced editing tools make it easy to take an initially created floorplan from Oasys, make changes and then iterate getting better versions multiple times per day. One of the most time consuming tasks in SoC/ASIC design is getting a good quality floorplan. Oasys floorplan compiler reduces the time required for this task from a typical 4-6 weeks down to a few days.

The underlying approach of the RealTime synthesis engine is that it optimizes at the RTL level using a placement first methodology. No timing is undertaken without the cells being placed, since in a modern process most of the timing is related to placement and routing and not just the basic cell timing. When timing constraints are not met, then instead of just running gate-level optimizations, the algorithms return to the RTL level and re-sythesize a local area of the design using the improved knowledge. A sort of rip-up and re-synthesize. This approach results in huge capacity (the whole gate-level netlist does not need to be processed at once) and incredibly short run-times (gate level optimization is very expensive and avoiding it saves most of the time taken by traditional synthesis). For floorplanning, this infrastructure makes it straightforward to optimize RTL partitions (and change them iteratively) and automatically place macros, pins and pads to create a high quality floorplan driven by the constraints provided.

The underlying approach of the RealTime synthesis engine is that it optimizes at the RTL level using a placement first methodology. No timing is undertaken without the cells being placed, since in a modern process most of the timing is related to placement and routing and not just the basic cell timing. When timing constraints are not met, then instead of just running gate-level optimizations, the algorithms return to the RTL level and re-sythesize a local area of the design using the improved knowledge. A sort of rip-up and re-synthesize. This approach results in huge capacity (the whole gate-level netlist does not need to be processed at once) and incredibly short run-times (gate level optimization is very expensive and avoiding it saves most of the time taken by traditional synthesis). For floorplanning, this infrastructure makes it straightforward to optimize RTL partitions (and change them iteratively) and automatically place macros, pins and pads to create a high quality floorplan driven by the constraints provided.

The input to Oasys RealTime Floorplan Compiler are the standard synthesis inputs (RTL, constraints, libraries) and the output is a standard floorplan DEF file which can either be fed into traditional synthesis tools or into place & route tools as an initial floorplan. So Floorplan Compiler drops seamlessly into existing flows.

More details on Floorplan Compiler are available here.

Oasys will be demonstrating Floorplan Compiler at DAC at booth 1231.

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!