Designing an LTE modem is an interesting case study in architectural and system level design because it is pretty much on the limit of what is possible in a current process node such as 28nm. I talked to Johannes Stahl of Synopsys about how you would accomplish this with the Synopsys suite of system level tools. He is the first to admit… Read More

Tag: synopsys

Test Compression and Hierarchy at ITC

The International Test Conference (ITC) is this week in Anaheim and I’ve just learned what’s new at Synopsys with test compression and hierarchy. Last week I spoke with Robert Ruiz and Sandeep Kaushik of Synopsys by phone to get the latest scoop. There are two big product announcements today that cover:… Read More

Mobile SoC will benefit now from M-PCIe

We have already discussed the recently released M-PCIe ECN from PCI-SIG in Semiwiki at the end of 2012, but the new “standard” (in fact an Engineering Change from PCI-SIG and MIPI Alliance) was only real on paper, at that time. The upcoming webinar from Synopsys, M-PCIe: Utilizing Low-Power PCI Express in Mobile Designs, shows … Read More

LSI’s Experience With Formality Ultra

LSI is an early adopter of Formality Ultra, Synopsys’s tool for improving the entire ECO flow. I already wrote about the basic capability of the tool here. ECOs are changes that come very late in the design cycle, after place and route has already been “nearly” completed. They occur either due to last minute spec… Read More

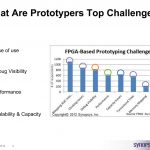

More to the story than bigger FPGA-based prototyping

Still not convinced on the value of FPGA-based prototyping systems, or using older technology? I’ve been trying to find the story beyond just bigger, badder FPGAs in a box that you pour RTL into – and found some hints in a webinar on the Synopsys HAPS-70 from earlier this year.… Read More

Why Adopt Hierarchical Test for SoC Designs

IC designers have been creating with hierarchy for years to better manage large design sizes, however for the test world the concept of hierarchy and emerging standards is a bit newer. TSMC and Synopsys jointly created a webinarthat addresses hierarchical test, so I’ve attended it this week and summarized my findings here.… Read More

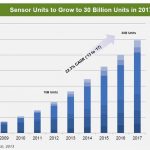

Pre-verified, Integrated Sensor IP Subsystem?

Last year, I said that the launch of ARC based complete sound system IP by Synopsys ring the bell for the opening of a new IP market segment, the “Subsystem IP”. This week, Synopsys has announced the availability of the DesignWare® Sensor IP Subsystem, a complete and integrated hardware and software solution for sensor control applications.… Read More

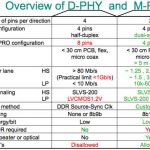

Any MIPI CSI-3 Host IP Solution for SoCs Interfacing with Sensors?

For those taking a quick look at the various MIPI Interface specification, the first reaction is to realize that they will have to look at MIPI more closely, and that it will take them longer than expected to make sure they really understand the various specifications! Let’s start with the PHY. One specification defines the D-PHY,… Read More

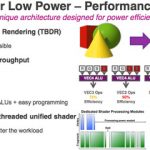

♫ IMG Sitting on the DOK of the Bay…Closin’ Timin’

Scott Fitzgerald is supposed to have said “the rich are not like other people” to Ernest Hemingway (he didn’t). In the same way, processors are not like other blocks, and not because they have more gates (they don’t). However, special approaches to optimizing processors are important because the clock… Read More

Debugging Verification Constraints

In his DAC keynote last year (2012) Mike Mueller of ARM compared how much CPU was required to verify the first ARM versus one of the latest ARM Cortex CPUs. Of course the newer CPU is hundreds of times larger than the first ARM but the amount of verification required was millions of times as much, requiring ARM to construct their own datacenter… Read More