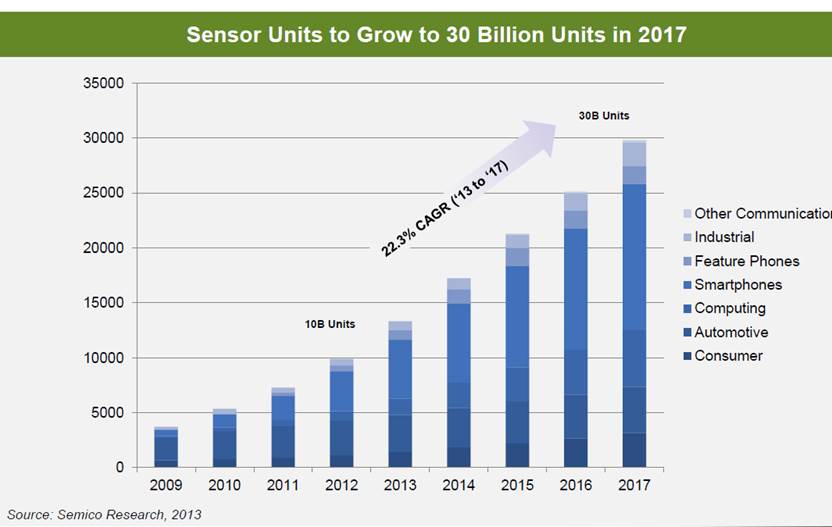

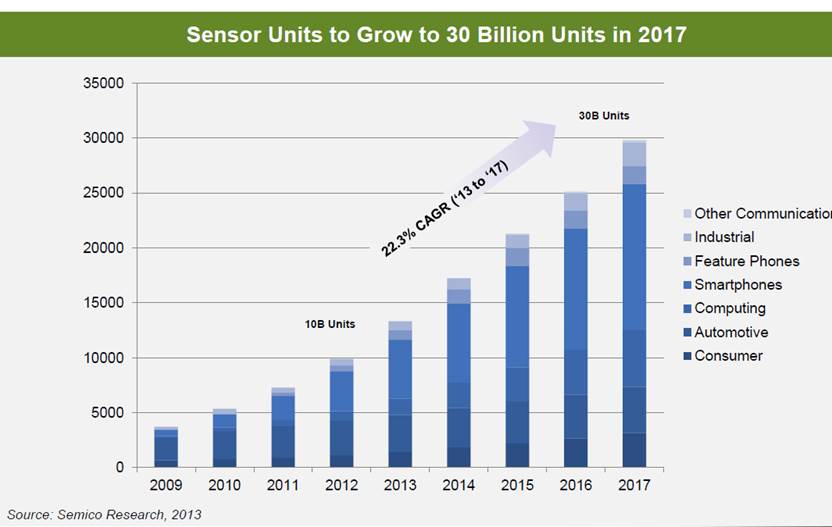

Last year, I said that the launch of ARC based complete sound system IP by Synopsys ring the bell for the opening of a new IP market segment, the “Subsystem IP”. This week, Synopsys has announced the availability of the DesignWare® Sensor IP Subsystem, a complete and integrated hardware and software solution for sensor control applications. This announcement is a step beyond the sound system IP, as we are talking now about a subsystem IP able to process data from multiple sensors, can be digital and analog, using Host Accelerators on top of ARC EM4 microcontroller, and generate a single output, accessible from the main SoC CPU via the host interface. If we look at the Total Addressable Market for sensors, the figures looks incredible, as in 2017 there will be 30 Billion sensors shipped, or about four per single human being!

Fig. 1: Sensor Units Shipments 2009-2017 (Semico)

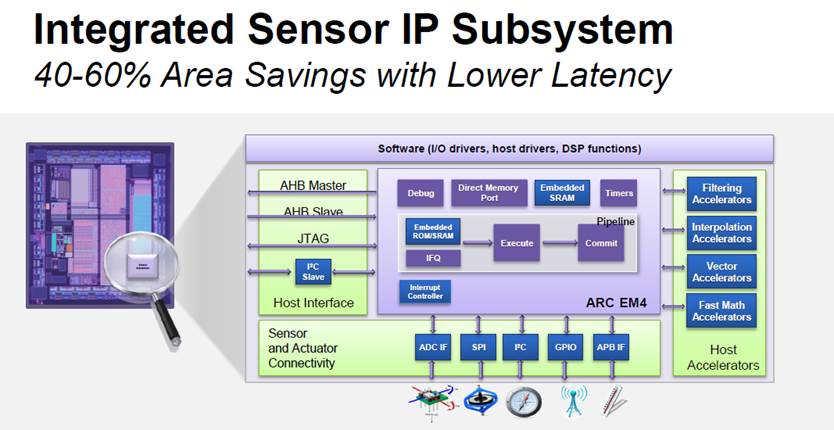

In fact, part of this TAM will be addressed by Standard IC sensor, and semiconductor suppliers like STM have already heavily invested into such product lines. But it is clear that, when OEM will need to lower the BOM cost, and reduce the number of chips in the system, or (and) reduce the overall system power consumption, integrating such a sensor subsystem into a larger SoC, like an Application Processor or a companion chip for smartphone, will be a must. The fully configurable subsystem consists of a DesignWare ARC[SUP]®[/SUP]EM4 32-bit processor, digital interfaces, analog-to-digital data converters (ADCs), hardware accelerators, a comprehensive software library of DSP functions and software I/O drivers.

Synopsys claim incredibly high gain, both in term of power and area. Like, for example, implementations as small as 0.01mm[SUP]2[/SUP], consuming less than 4uW/MHZ in a 28-nm process! I have mentioned wireless applications, in fact we can see from the Sensor Shipment forecast on figure 1 that this subsystem IP sensor may be used in many other segments: Consumer, Automotive, Computing or Industrial. This is illustrated by the quote from Robert Fortin, director of sensors business unit at Allegro Microsystems, LLC: “As the technology leader in magnetic sensor ICs for the automotive market, it is critical that Allegro acquires high-quality IP from a trusted provider such as Synopsys”. “Based on our experience, the DesignWare ARC 32-bit processor’s combination of high performance, small area and low power provides key advantages for sensor design over alternative solutions.”

Fig. 2: Integrated Sensor IP Subsystem

Considering the massive trend to system integration onto a single, or a couple of chips, delivering an hardware solution like a “LEGO” kit solution is not anymore sufficient. This solution need to be pre-verified, the design team integrating the hardware having to verify only the connectivity inside the SoC. As well, the software should be delivered, and be pre-verified too, and S/W DSP libraries be part of the delivery kit. To be successful, such a subsystem IP has to be highly configurable, the dedicated hardware and peripherals being tightly integrated (by the supplier, not the design team), in order to maximize both the sensor processing efficiency, and the SoC development time, that is the Time To Market. Because this solution tend to be really complete, extensive library of off-the-shelf software DSP functions, including mathematical, filtering, matrix/vector and decimation/interpolation, speeds application software development .

Let John Koeter, vice president of marketing for IP and systems at Synopsys, give the conclusion: “The industry is seeing significant proliferation of sensor-enabled devices in homes, cars and on-the-go. These devices require integrated sensor SoCs that deliver high performance, small area and low power consumption. Synopsys’ pre-verified, SoC-ready sensor subsystem provides designers with a higher level of hardware and software IP integration, enabling them to achieve their design goals faster and with significantly less risk.”

By Eric Esteve

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.