The International Test Conference (ITC) is this week in Anaheim and I’ve just learned what’s new at Synopsys with test compression and hierarchy. Last week I spoke with Robert Ruiz and Sandeep Kaushik of Synopsys by phone to get the latest scoop. There are two big product announcements today that cover:

- Test compression with DFTMAX Ultra, about 2-3X higher compression which combined with fewer test pins and faster scan speeds can reduce test cost by 20X

- STAR Hierarchical system, reduces SoC test times by weeks

Robert Ruiz

Sandeep Kaushik

DFTMAX Ultra

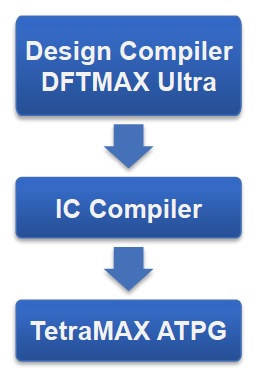

Synopsys started offering test compression on-chip in 2005 with the DFMTAX product, and now they’ve totally revamped it with the new DFTMAX Ultra. It’s built inside of DesignCompiler, so it’s usable by either design engineers or test engineers.

Design and Test Flow

DFTMAX Ultra

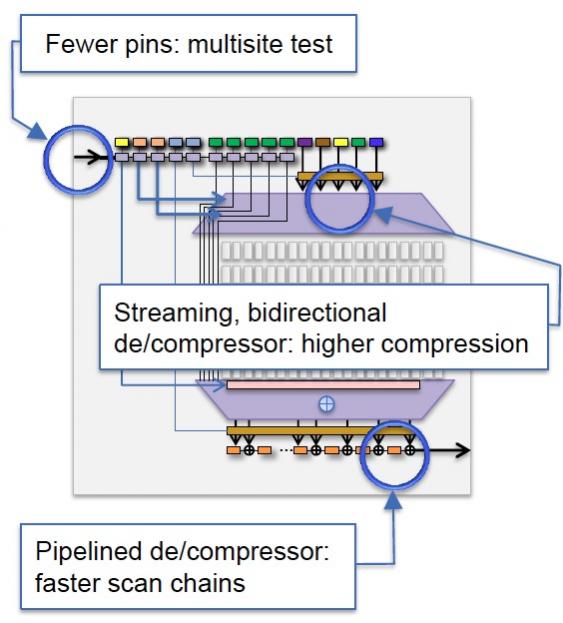

We first started hearing about DFTMAX Ultra at DAC, and now it’s finally here. Compared to DFTMAX you’ll see:

- 2 to 3X higher compression, giving you shorter test times

- Subtle defect detection (resistive bridge, metal void, FinFET opens, litho hotspots)

- Fasert scan chains, think 60MHz

- Multisite test, doing two tests at once in parallel

Initial quotes from customers like Realtek and STMicroelectronic validate the test cost reductions.

Since DFTMAX Ultra is a new product, you’ll have to contact the local Synopsys account manager for pricing, and AE for training. The learning curve is minimal maybe a few hours, although the HW architecture is different and the UI is updated. Early customers have been using this tool for the past year, so we’ll see tape outs from DFTMAX Ultra this year. Run times are even faster with DFTMAX Ultra, maybe a 10-50% improvement. Patents are pending, and unlike other areas of EDA there are no active or pending lawsuits over this compression technology.

Expect continued support of DFTMAX for quite a while.

STAR Hierarchical System

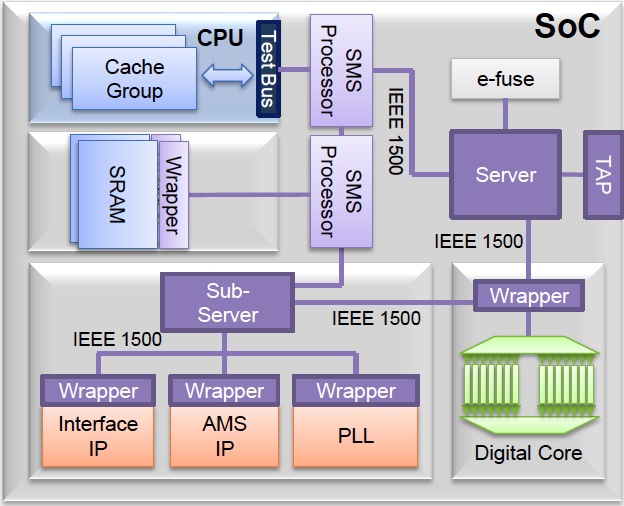

This new test tool offers a way to accelerate SoC testing while improving the test QoR. The STAR Hierarchical System is different because it uses the IEEE 1500 and 1149.1 standards, versus other approaches, and it allows the test engineer to integrate any type of IP block or core into an SoC for maximum testability. It’s also built on expertise in designing IP at Synopsys. There is lots of control on how to schedule tests, and silicon repair is also supported for things like AMS IP blocks.

The areas in dark purple above denote the new STAR Hierarchical System, while the light purple boxes are for the STAR Memory System.

The main benefits of using this test approach on your next SoC are:

- Saving weeks of IP and core integration

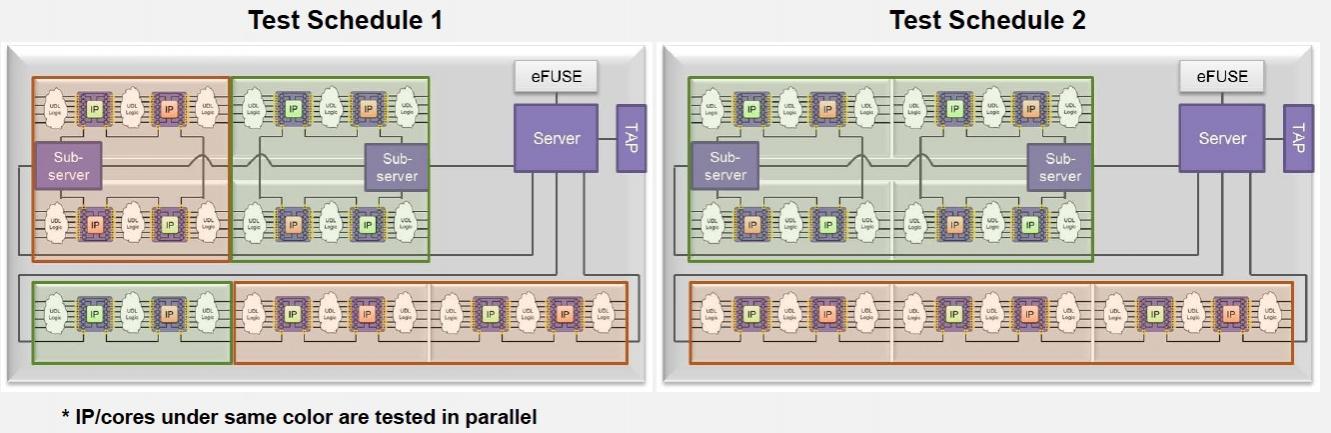

- Shorten test times by running IP blocks or cores in parallel

- Reusing your existing IP and core patterns

- Quicker time to production ramp by using silicon memory repair and failure diagnostics

An SoC today may have 100M gates, over 150 IP blocks, and require 400 or more engineers. Using a test bus in a structured approach with hierarchy is a practical approach to meet SoC test challenges.

Test scheduling enables parallel operation, shortening test times

STMicroelectronics confirms that you can save weeks of test development time, and even within Synopsys they’ve made their own IP compatible ready for use with the STAR Hierarchical System:

- USB

- MIPI

- HDMI

- SATA

- PCIe

- DDR

- Memory

The STAR Hierarchical System is easy to learn because it uses test standards like IEEE 1500, and if you have used STAR memory before then you can become proficient in a few days. Contact your local Synopsys AE to get started, or attend a training course to learn more about this.

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.