Before going to Munich to attend to CDN-Live, I took a look at the agenda to figure out which presentations to attend, and I must say it was not so easy to choose: CDN Live agendais dense, with multiple tracks running in parallel (Custom Design, Digital Implementations, Design IP, Functional Verifications and Verification IP, PCB… Read More

Tag: cadence

Semiconductor Ecosystem Keynotes: ARM 2012

Yesterday’s SEMICO IP Ecosystem Conference was well worth the time. Everybody was there: ARM, Synopsys, Cadence, Mentor Graphics, GlobalFoundries, TSMC, MIPS, Tensilica, AMD, Atrenta, Sonics, and Tabula, everybody except Intel of course. What do Intel and I have in common? We don’t play well with others…

First up was… Read More

Cadence Update 2012!

What’s new at Cadence? Quite a bit actually. I have always been a Cadence fan, I mean really, they gave birth to modern EDA. Unfortunately, Cadence really lost me during the Avant! legal action, the Mike Fister years, and EDA360. Recently, however, Cadence has made some big changes that will definitely get them back on my good side.… Read More

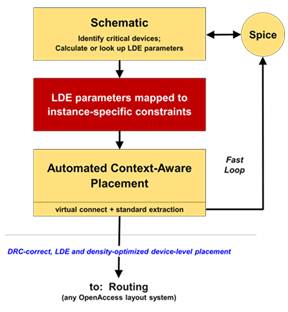

28nm Layout Needs Signoff Quality at Design Time

We are all aware that at 28nm and below several types of complex layout effects manifest themselves into the design and pose a herculean task, with several re-spins to correct them at pre-tapeout. It’s apparent that the layout needs to be correct by construction at the very beginning during the design stage.

20nm IC Design at IBM using Cadence Tools

Collaboration between EDA, Foundry and Design was the key idea today in a webinar hosted by IBM and Cadence about 20nm custom IC design. The three presenters were:

John Stabenow, Cadence

Jeremiah Cessna, Cadence

Keith Barkley, IBM… Read More

GSA 3DIC and Cadence

At the GSA 3D IC working group meeting, Cadence presented their perspective on 3D ICs. Their view will turn out to be important since the new chair of the 3D IC working group is going to be Ken Potts of Cadence. Once GSA decided the position could not be funded then an independent consultant like Herb Reiter had to bow out and the position… Read More

A Simple, Scalable LDE Optimization Flow for 28/20nm Custom/AMS Design

At 28nm and below, a number of electrical variation effects become significant which depend not only on individual devices, but the physical interaction between neighboring devices, wells, etc during the manufacturing process. Some of these effects have become collectively referred to as “Layout Dependent Effects” (LDE);… Read More

Kadenz Leben: CDNLive! EMEA

If you are in Europe then the CDNLive! EMEA user conference is in Munich at the Dolce Hotel from May 14th to 16th. Like last month’s CDNLive! in Cadence’s hometown San Jose, the conference focuses on sharing fresh ideas and best practices for all aspects of semiconductor design from embedded software down to bare silicon.… Read More

Smart mobile SoCs: Texas Instruments

TI has parlayed its heritage in digital signal processing and long-term relationships with mobile device makers into a leadership position in mobile SoCs. They boast a relatively huge portfolio of design wins thanks to being the launch platform for Android 4.0. On the horizon, the next generation OMAP 5 could change the entire… Read More

I Love DAC

For the fourth year Atrenta, Cadence and Springsoft are jointly sponsoring the “I LOVE DAC” campaign. In case you have been hibernating all winter, DAC is June 3-7th in San Francisco at the Moscone Center.

There are two parts to “I LOVE DAC”. First, if you register by May 15th (and they haven’t all… Read More