You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The problem:To move dual-port SRAM library and macros from a 40nm process to a 28nm process. In addition to all the changes between two different foundry processes, the 28nm rules are disruptive and incompatible with the previous rules. The memory corecells (foundry-specific) would also need to be completely replaced.

Current… Read More

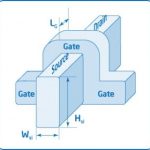

Intel had a big press event yesterday at which they announced details of their 22nm process. In a change from their current processes, it goes with a vertical gate. In fact 3 gates which gives them much better control of leakage through transistors that are switched off, along with more transmission through the on transistors. They… Read More

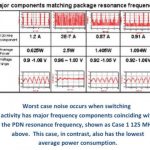

As the complexity of the chip-package-system (CPS) interactions has increased, the tradeoffs in doing a power and noise analysis has had to gradually increase. As is so often the case in semiconductor designs, issues first arise as second-order effects that can largely be ignored but each process node makes the problem worse … Read More

Apache at DACby Paul McLellan on 05-04-2011 at 2:38 pmCategories: Ansys, Inc., EDA

DAC is less than a month away, June 6-8th for the tradeshow, longer depending on what other events you might also be attending. Apache is in booth 2448 (marked in red on the DAC floorplan map.

Many of the presentations at the Apache booth will be customers (such as ARM, Xilinx, ST Ericsson, GlobalFoundries and TSMC) discussing various… Read More

Introduction

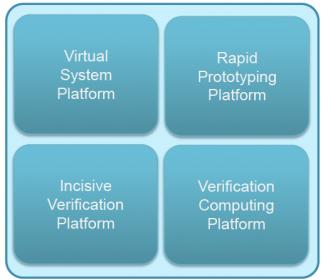

Today Cadence announced at the Embedded Systems Conference something of interest to systems designers.

What’s New?

The Rapid Prototyping Platform and Virtual System Platform are what’s new, and they intend to enable and automate concurrent hardware and software development. I can remember Mentor… Read More

Although there has been always a strong relationship between Kilopass and Chartered Semiconductor, this relationship has been even enhanced after the acquisition of Chartered by GLOBALFOUNDRIES, allowing Kilopass’s customers to integrate NVM IP on advanced technology nodes, down to 40nm or even 28nm in the near future.

Before… Read More

Introduction

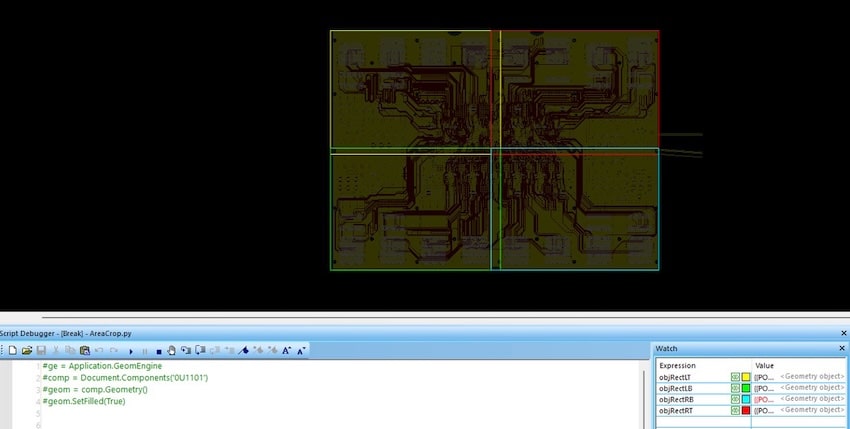

IC designs go through a layout process and then a verification of that layout to determine if the layout layer width and spacing rules conform to a set of manufacturing design rules. Adhering to the layout rules will ensure that your chip has acceptable yields.

At the 28nm node a typical DRC (Design Rule Check) deck will… Read More

Mentor 2 : Carl Icahn 0by Daniel Nenni on 05-01-2011 at 9:46 amCategories: EDA

The corporate raiders are still throwing rocks at Mentor Graphics. I have followed this reality show VERY closely and find their latest assault seriously counterproductive. Disinformation is common in EDA but I expected more from Carl Icahn and the Raiderettes. They are quite the drama queens. Here is a billion dollar question:… Read More

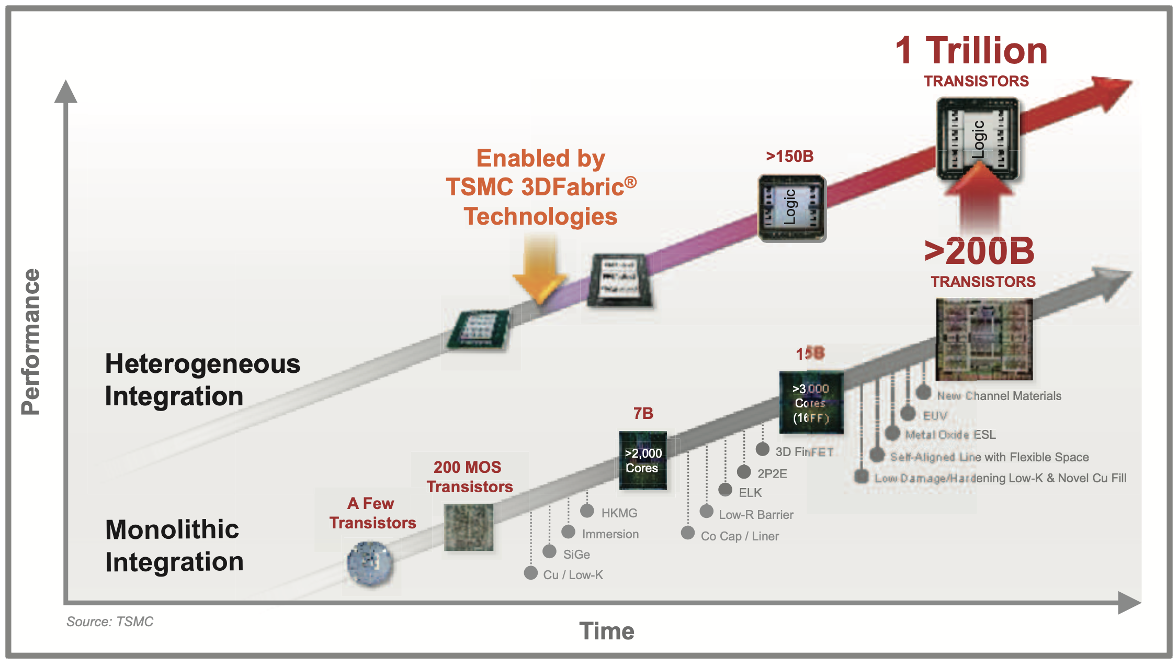

TSMC continues to drive the economic recovery with impressive Q1 numbers and an even more impressive Q2 and Q3 outlook. TSMC is my economic bellwether due to its diverse customer base and shear volume of consumer electronics silicon. The big surprise in the 1 hour Q1 conference call is a new Giga Fab (#15) ground breaking this year… Read More

I was at Mentor’s u2u (user group) meeting and one of the keynotes was by Ivo Bolsens of Xilinx. The other was by Wally Rhines and is summarized here.

Ivo started off talking analogizing SoCs as the sports-cars of the industry (fast but expensive), and FPGAs as the station wagons (not cool). In fact he even said that when Xilinx… Read More

If you believe in Hobbits you can believe in Rapidus