Earlier this week I moderated a webinar at Sonics entitled NoC 102: Using SonicsGN to Address Low Power Requirements. Drew Wingard, the CTO of Sonics, presented it. It goes without saying that power is a major concern in SoC design, not just with chips for battery powered devices but also tethered devices. A major cost of ownership… Read More

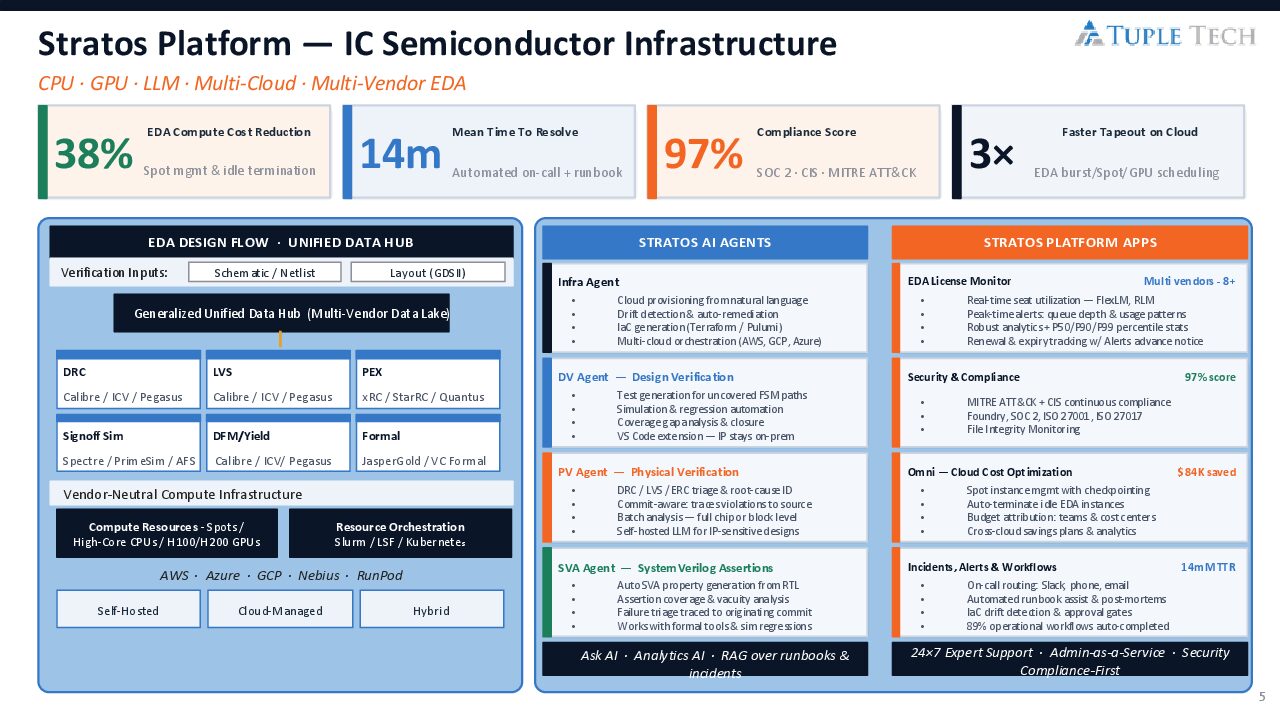

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreTSMC vs Samsung!

One of the trending topics in Taiwan last week is the escalating conflict between Samsung and TSMC. This time however it is of a legal nature which has been a long time coming for the semiconductor industry. Reverse engineering has been an integral part of the semiconductor business since the beginning, as has intellectual property… Read More

Sony Endorse FD-SOI to Attack Wearable & IoT

We are writing about FD-SOI technology since the beginning of 2013 in Semiwiki. So far, most of the design experience was related to ST-Microelectronics (even if IBM and GlobalFoundries have been actively working on the technology, probably more on a research mode than pure production). Sony being actively working to develop… Read More

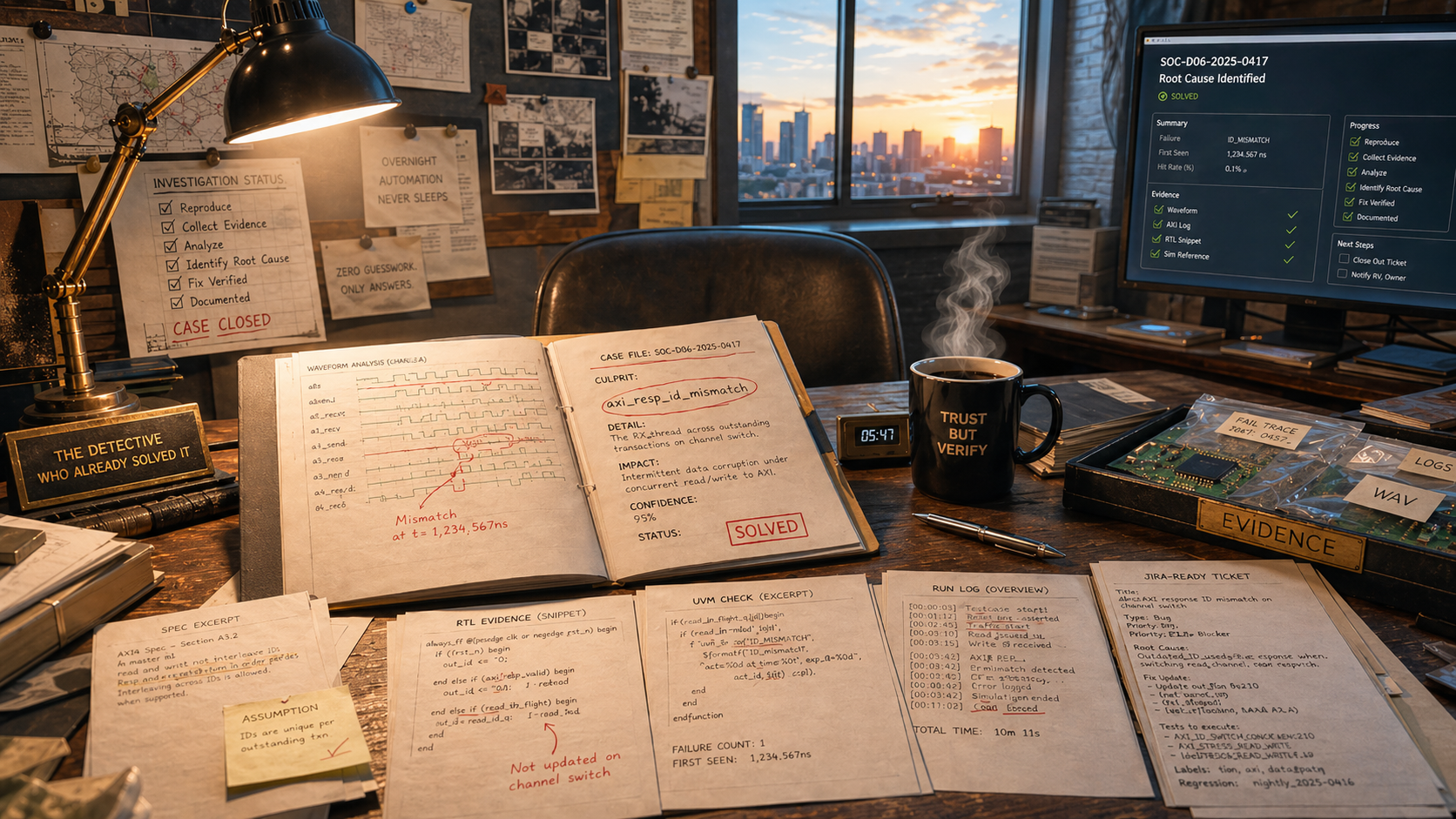

Chips Are Going 3D, DRC Needs to Go 3D Too

The last paradigm shift in DRC was around 0.35um when designs got too large to handle as flat data, and hierarchical approaches were required. Back then the design rules themselves were not that complex, the explosion of data volume came from the complexity of the design itself. But each process node added more design rules intricacies… Read More

Open Forum for Semiconductor Professionals!

The semiconductor industry has never been more exciting than it is today, at least not in my 30 years of experience. Things are moving faster than ever before making collaboration at all levels a requirement. At SemiWiki we are afforded the privilege of passes to semiconductor conferences around the world. We also have access to… Read More

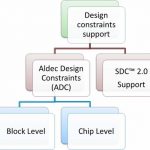

Writing the unwritten rules with ALINT-PRO-CDC

EDA verification tools generally do a great job of analyzing the written rules in digital design. Clock domain crossings (CDCs) are more like those unwritten rules in baseball; whether or not you have a problem remains indefinite until later, when retaliation can come swiftly out of nowhere.

Rarely as overt or dramatic as a bench-clearing… Read More

A Public Synchronizer

You might ask yourself “Why would anyone want to have a public synchronizer available to download?” Usually designers just grab a flip-flop from his or her company’s or a standard cell vendor’s library. However, are these handy solutions the best course of action today? Current SoC designs have numerous clock domains providing… Read More

Webinar: How IoT Designs Driven by Cost Power Security

SoCs being developed for the fast growth Internet-of-Things market will sell for and operate on a small fraction of the power of mobile devices’ chips. More importantly, IoT SoCs will be far more vulnerable to hacker attacks than the much better protected chips in portable devices. As a result, designers developing SoCs targeting… Read More

Integrated Spec Design & Documentation for SoC

One challenge in SoC projects is maintaining consistency between the specification, design and documentation throughout the product lifecycle. Imagine the chaos if your specification for power is 300 mW, the design is actually 350 mW and the documentation promises 250 mW. Traditionally the design and documentation process… Read More

FD-SOI at Samsung

Various foundries have made announcements about licensing FD-SOI technology from ST Microelectronics and then fallen quiet. GlobalFoundries made an announcement a couple of years ago. Samsung made an announcement just before DAC last year. But neither company has said anything much since. Of course the big noise at 14/16nm… Read More

Siemens U2U 3D IC Design and Verification Panel