Last Thursday night was the 20[SUP]th[/SUP] annual GSA Awards Dinner which probably hosts one of the largest collections of semiconductor executives. Think of a movie or music awards show with all of the trimmings including Jay Leno as the keynote. I don’t know the exact head count but there were 160 dinner tables with 10 plates … Read More

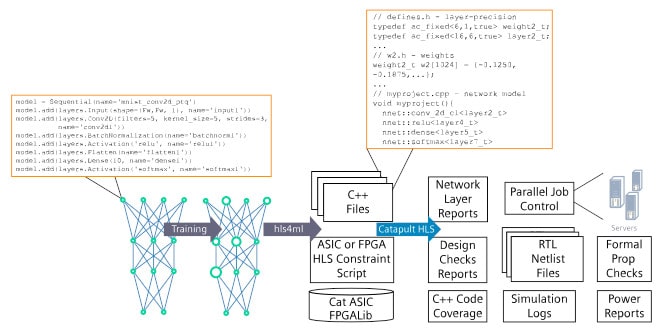

New Tool that Synthesizes Python to RTL for AI Neural Network CodeAI and ML techniques are popular topics, yet…Read More

New Tool that Synthesizes Python to RTL for AI Neural Network CodeAI and ML techniques are popular topics, yet…Read More S2C and Sirius Wireless Collaborate on Wi-Fi 7 RF IP Verification SystemSirius Wireless partnered with FPGA prototyping expert S2C…Read More

S2C and Sirius Wireless Collaborate on Wi-Fi 7 RF IP Verification SystemSirius Wireless partnered with FPGA prototyping expert S2C…Read MoreVirtual Emulation Extends Debugging Over Physical

Amid burgeoning complexity of SoC verification with ever increasing hardware, software and firmware content, verification engineers are hard pressed with learning multiple tools, technologies and methodologies and still completing SoC verification with full accuracy in time. The complexity, size and diversity of SoC … Read More

Will 3DIC Ever Be Cheap Enough for High Volume Products?

More news from the 3DASIP conference. Chet Palesko of SavanSys Solution had an interesting presentation with the same title as this blog (although this blog draws from several other presentations too). Chet took a look at what aspects of 3D are likely to get cheaper going forward. He took as a starting point that stuff that is not … Read More

Benefits of Using Schematic Driven Layout

Most IC designs are developed by a team of professionals, often separated into distinct groups like front-end and back-end, logical and physical designers. Circuit designers use tools like schematic capture at the transistor-level to create a topology, then begin simulating the netlist with a SPICE simulator. Layout designers… Read More

3D, The State of the State

I have been at the 3D ASIP conference that is held every year in Burlingame. It is far and away the best place to get a snapshot on what is going on in 3D (and 2.5D) IC design each year. One of the presentations was by the guys from Yole on where the industry is right now. Other presentations were on pathfinding, power reduction (did you know… Read More

A Functional Verification Framework Spanning Simulation to Emulation

Software engineers and firmware designers can find bugs, update their code and re-distribute to the users. In the consumer electronics world this means that my smart phone apps get updated, and my Android OS gets updated on a somewhat regular basis, however on the hardware side the design and verification of an SoC must be close … Read More

IDT bolsters RF portfolio amid LTE boom

The global rollout of fourth-generation wireless (4G) infrastructure requires new architectural frameworks for RF devices with demands like high linearity. Integrated Device Technology (IDT) Inc. is confident that its high-performance RF solutions for high-bandwidth communications will open a new window of opportunity… Read More

TSMC Gets Ready for IoT

With all the talk about 14/16nm and 10nm it is important to realize that older processes are still important. Eventually 16nm may end up being cheaper than 28nm but for the time being 28nm seems to be a sort of sweet spot, not just cheaper than every process that came before it (which was true for every new node) but also cheaper than every… Read More

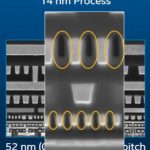

Intel has Another First for 14nm Production!

An interesting thing happened while I was researching a slide from Bill Holt’s “Advancing Moore’s Law” presentation at last month’s analyst meeting. Slide #19 mentioned that Intel was the first to use “air gap” dielectric spaces to improve performance in a digital logic flow for microprocessors. I know a certain foundry that … Read More

CTO Interview with Dr. Wim Schoenmaker of Magwel

I visited the Magwel booth at DAC in June and chatted with Dundar Dumlugol the CEO about their EDA tools that enable 3D co-simulation and extraction. Since then I’ve made contact with their CTO, Dr. Wim Schoenmaker to better understand what it’s like to start up and run an EDA company. Magwel’s history goes back… Read More

Ncredible Nvidia