Hyperscale data centers are evolving rapidly to meet the demands of high-bandwidth, low-latency applications, ranging from AI and high-performance computing (HPC) to telecommunications and 4K video streaming. The increasing need for faster data transfer rates has prompted a scaling of Ethernet from 51Tb/s to 100Tb/s. Numerous… Read More

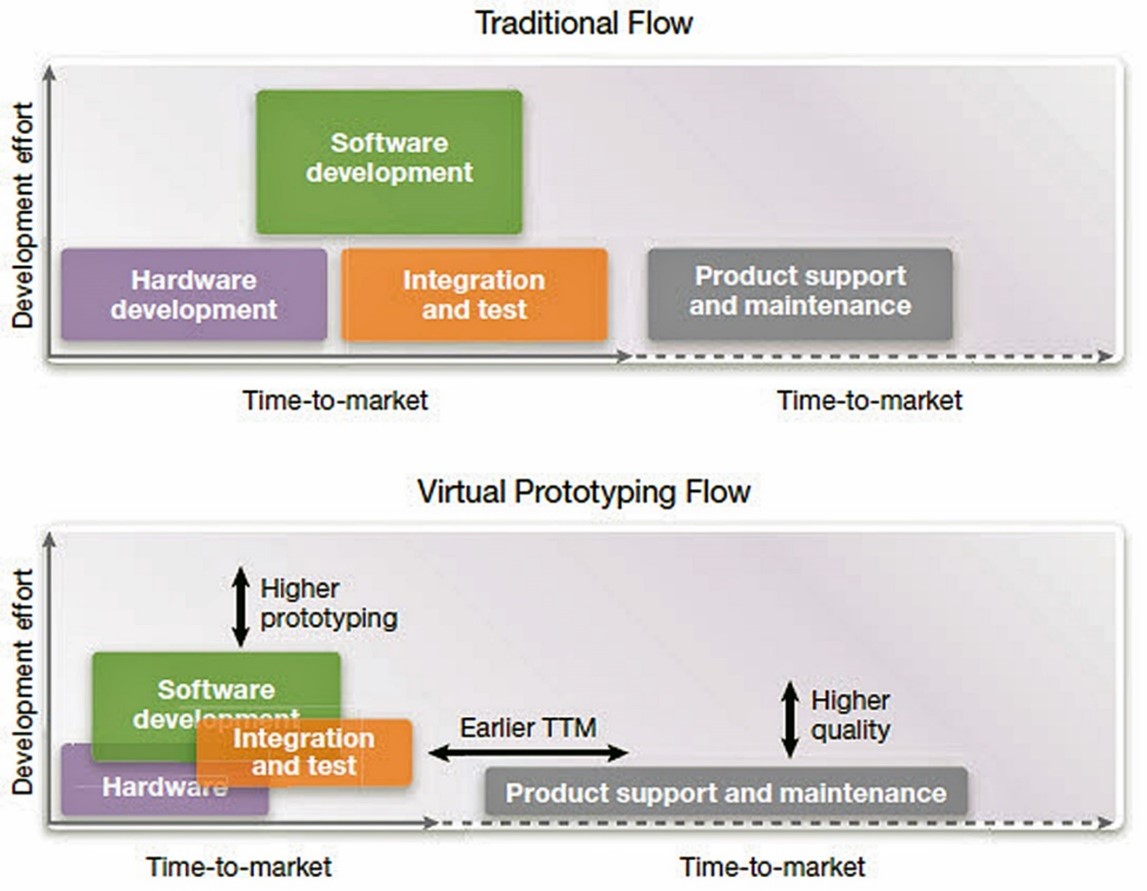

The Immensity of Software Development and the Challenges of Debugging Series (Part 2 of 4)Part 2 of this 4-part series reviews the…Read More

The Immensity of Software Development and the Challenges of Debugging Series (Part 2 of 4)Part 2 of this 4-part series reviews the…Read More Collaboration Required to Maximize ASIC Chiplet ValueIt is a well-known fact that chiplets provide…Read More

Collaboration Required to Maximize ASIC Chiplet ValueIt is a well-known fact that chiplets provide…Read More Andes Technology is Expanding RISC-V’s Horizons in High-Performance Computing ApplicationsBy: Dr. Charlie Su, President and CTO, Andes…Read More

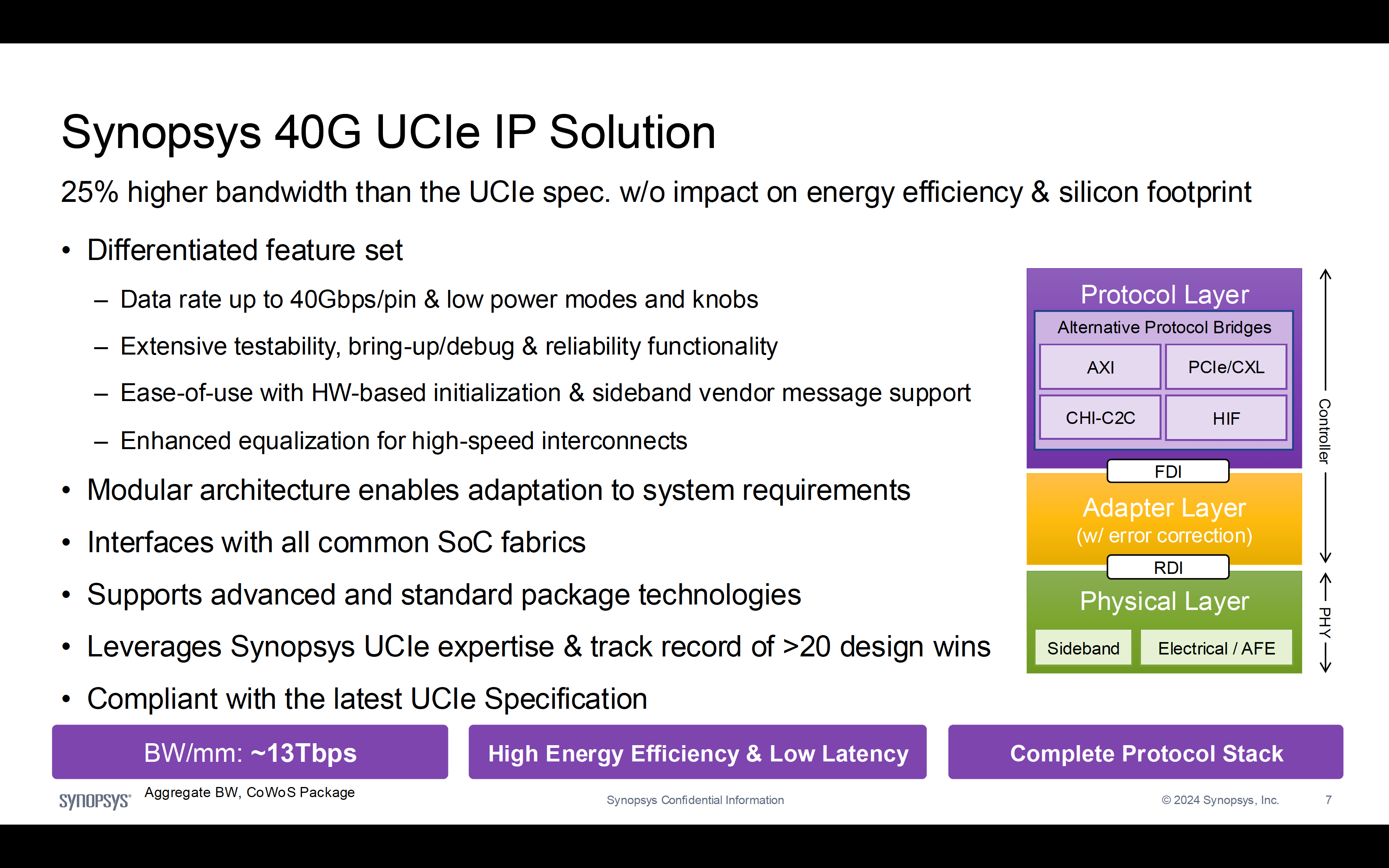

Andes Technology is Expanding RISC-V’s Horizons in High-Performance Computing ApplicationsBy: Dr. Charlie Su, President and CTO, Andes…Read More Synopsys Powers World’s Fastest UCIe-Based Multi-Die Designs with New IP Operating at 40 GbpsAs the demand for higher performance computing solutions…Read More

Synopsys Powers World’s Fastest UCIe-Based Multi-Die Designs with New IP Operating at 40 GbpsAs the demand for higher performance computing solutions…Read MorePodcast EP195: A Tour of Mythc’s Unique Analog Computing Capabilities with Dave Fick

Dan is joined by Dave Fick, co-founder and CEO of Mythic. Dave leads Mythic to bring groundbreaking analog computing to the AI inference market. With a PhD in Computer Science & Eng from Michigan, he brings a wealth of knowledge and expertise to the industry.

Dan explores Mythic’s unique analog computing capability … Read More

CEO Interview: Dr. Meghali Chopra of Sandbox Semiconductor

Dr. Meghali Chopra is co-founder and CEO of SandBox Semiconductor. She is responsible for SandBox’s vision and strategy and oversees the development of SandBox’s software products and technologies. Dr. Chopra received her PhD in Chemical Engineering from the University of Texas at Austin where her research focused … Read More

Generative AI for Silicon Design – Article 4 (Hunt for Bugs)

In the complex world of silicon design, ensuring the accuracy and reliability of our designs is paramount. As our chips become more sophisticated, the process of bug hunting—identifying and rectifying errors in our designs—becomes even more critical. Generative AI has the potential to revolutionize the silicon design industry… Read More

Handling metastability during Clock Domain Crossing (CDC)

SoC designs frequently have lots of different clock domains to help manage power more efficiently, however one side effect is that when the clock domains meet, i.e., in a Clock Domain Crossing (CDC), there’s the possibility of setup and hold time violations that can cause a flip-flop to become metastable. Synchronizer … Read More

Predicting Stochastic Defectivity from Intel’s EUV Resist Electron Scattering Model

The release and scattering of photoelectrons and secondary electrons in EUV resists has often been glossed over in most studies in EUV lithography, despite being a fundamental factor in the image formation. Fortunately, Intel has provided us with a laboriously simulated electron release and scattering model, using the GEANT4… Read More

Navigating Edge AI Architectures: Power Efficiency, Performance, and Future-Proofing

The surge in Edge AI applications has propelled the need for architectures that balance performance, power efficiency, and flexibility. Architectural choices play a pivotal role in determining the success of AI processing at the edge, with trade-offs often necessary to meet the unique demands of diverse workloads. There are… Read More

Cadence Integrates Power Integrity Analysis and Fix into Design

As integration levels increase, clock frequencies rise, and feature sizes shrink it is not surprising that all or most aspects of semiconductor design become more complex and demand more from design technologies. One example where the traditional approach is breaking down is in optimizing power distribution networks (PDNs)… Read More

Webinar: Silicon Catalyst & EE Times Examine the Bigger Picture Aspects of AI – Nov. 29, 2023 – 9am to 10am Pacific

Artificial Intelligence (AI) is dominating the news cycle these days. It used to be about the latest (and largest) chips to accelerate AI algorithms. While that’s still relevant and exciting, AI news is taking a much broader, socioeconomic character. What does AI mean for job security, the economy, or even life on Earth? These … Read More

China’s hoard of chip-making tools: national treasures or expensive spare parts?

In the closing scene of Steven Spielberg’s Raiders of the Lost Ark (1981), the camera pulls back to reveal an enormous warehouse stacked with crates of artifacts hidden away by the US government.

One could imagine a similar warehouse in China today. The crates would hold a different kind of treasure – semiconductor production … Read More

5 Expectations for the Memory Markets in 2025