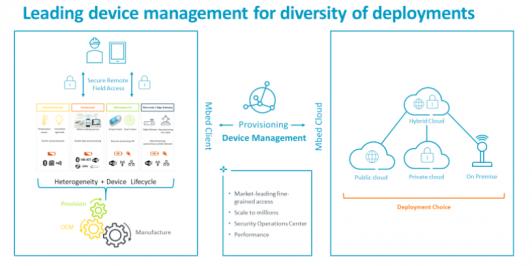

Normally press release events with ARM tend to be somewhat arms-length – a canned pitch followed by limited time for Q&A. Through a still unexplained calendar glitch I missed a scheduled call for a recent announcement. To make up I had the pleasure of a 1-on-1 with Hima Mukkamala, GM of IoT cloud services at ARM. Hima is a heavy … Read More

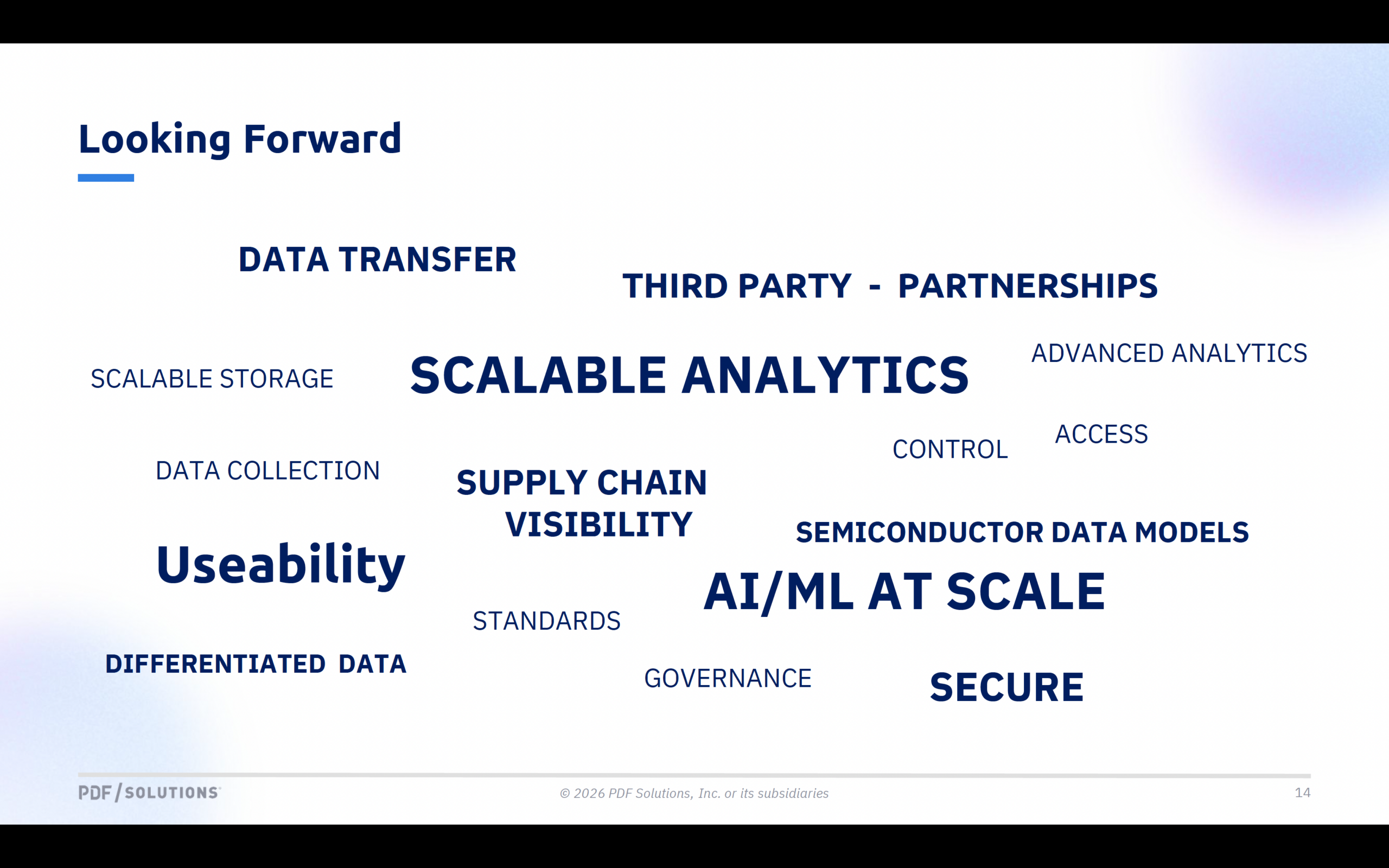

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More

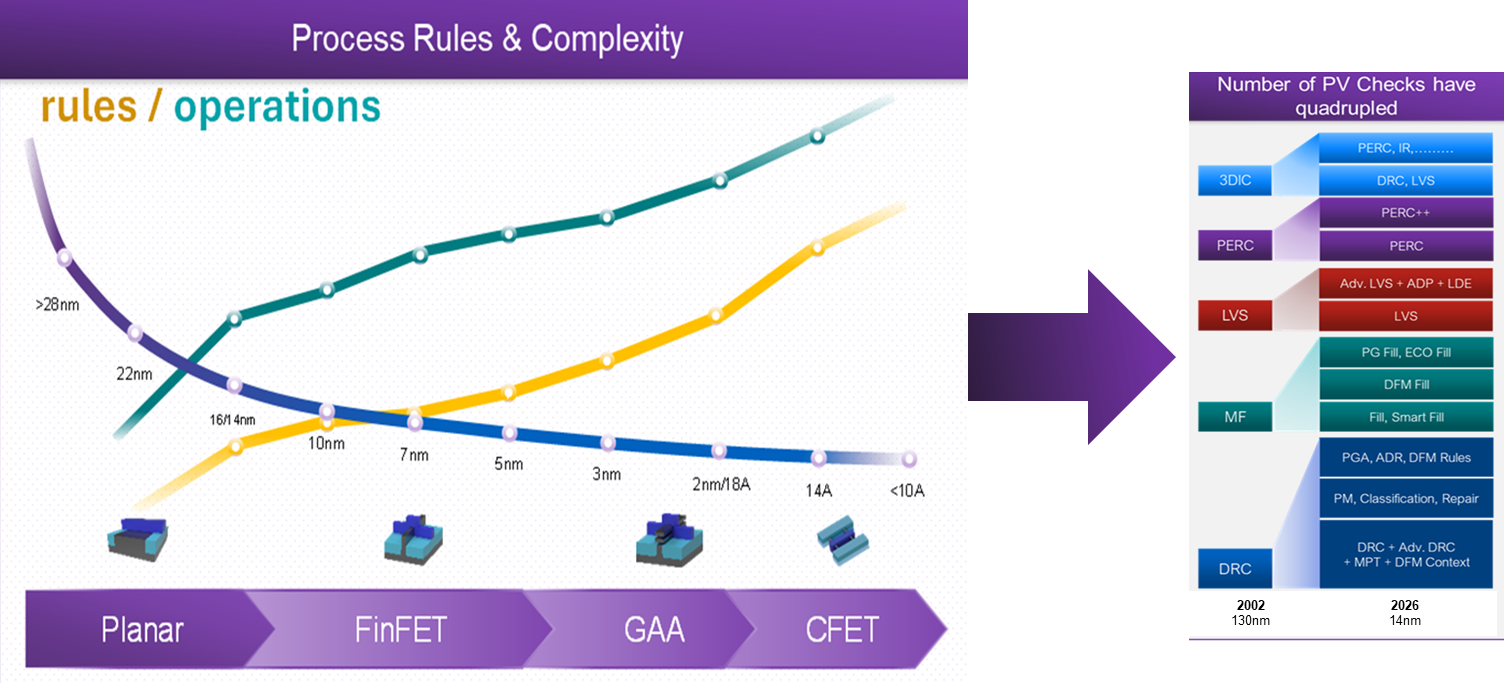

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More

How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read MoreHard IP for an embedded FPGA

As Moore’s Law enables increased integration, the diversity of functionality in SoC designs has grown. Design teams are seeking to utilize outside technical expertise in key functional areas, and to accelerate their productivity by re-using existing designs that others have developed. The Intellectual Property (IP) industry… Read More

imec and Cadence on 3nm

One of the more frequent questions I get, “What is next after FinFETs?” is finally getting answered. Thankfully I am surrounded by experts in the process technology field including Scotten Jones of IC Knowledge. I am also surrounded by design enablement experts so I really am the man in the middle which brings us to a discussion between… Read More

Intel 10nm Yield Issues

On their first quarter earnings call Intel announced that volume production of 10nm has been moved from the second half of 2018 to 2019 due to yield issues. Specifically, they are shipping 10nm in low volume now, but yield improvement has been slower than anticipated. They report that they understand the yield issues but that improvements… Read More

Data Center Powers Intel but 10NM Still Slow

Intel (INTC) blew away expectations based on strong performance in the data center. Revenues of $16.1B versus street of $15.05B and EPS of $0.93 versus street of $0.72. While revenue was up 9% over prior year, earnings were 50% higher. Guidance is for Q2 revenue of $16.3B and EPS of $0.85 versus street of $15.55B and EPS of $0.81. IOT,… Read More

Samsung has another record quarter in chips

Samsung throws further gas on the fire of weak handset and CAPEX not set but will be down versus 2017. Samsung reported revenues of KRW 60.56 Trillion and KRW 15.64 Trillion operating profit ($56B and $15B). Chips accounted for whopping KRW 11.55 Trillion in operating profit on revenues of KRW 20.78 Trillion ( $11B and $19B)….a… Read More

Webinar: ASICs Unlock Deep Learning Innovation

In March, an AI event was held at the Computer History Museum entitled “ASICs Unlock Deep Learning Innovation.” Along with Samsung, Amkor Technology and Northwest Logic, eSilicon explored how these companies form an ecosystem to develop deep learning chips for the next generation of AI applications. There was also a keynote … Read More

Achronix Momentum Building with Revenue Growth, Product/Staff Expansion, New HQ

5G Wireless, Network Acceleration, Data centers, Machine Learning, Compression, Encryption fueling the Growth

Building on its increasing momentum, Achronix Semiconductor Corporation held a ribbon-cutting ceremony on Tuesday, April 25, with the presence of Santa Clara’s Mayor Lisa Gillmor, customers, and partners, employees… Read More

Monitoring Process, Voltage and Temperature in SoCs, webinar recap

Have you ever wondered how process variation, thermal self-heating and Vdd levels affect the timing and yield of your SoC design? If you’re clock specification calls for 3GHz, while your silicon is only yielding at 2.4GHz, then you have a big problem on your hands. Such are the concerns of many modern day chip designers. To… Read More

Open-Silicon, Credo and IQ-Analog Provide Complete End-to-End Networking ASIC Solutions

The end-to-end principle as defined by Wikipedia is a design framework in computer networking. In networks designed according to this principle, application-specific features reside in the communicating end nodes of the network, rather than in intermediary nodes, such as gateways and routers, that exist to establish the … Read More

Is Intel About to Take Flight?