Something I always admire about Mentor is their willingness to invest their time and money in helping the industry at large. They do this especially in verification where they sponsor periodic Wilson surveys on the state of verification needs and usage in the industry. More recently they introduced their UVM Cookbook, an introduction to help new users and also I’m sure a handy reference to the more arcane corners of the standard for experienced UVM practitioners. Of course a challenge in any how-to guide to an evolving standard is that it inevitably drifts out of date. So Mentor recently released an update, aligned with the IEEE 1800.2 release, which should encourage freshers to seniors to turn to this guide to learn, as a reference and to dip into as a great source of examples.

Check out the Mentor Webinar on September 11[SUP]th[/SUP] at 8am Pacific.

To help me out, Tom Fitzpatrick (Strategic Verification Architect at Mentor) and I first talked about where UVM adoption is these days. While older methodologies (“e”, VMM etc) still claim their adherents, based on the latest Wilson survey UVM is fast becoming the methodology of choice, especially in ASIC design but also starting to see traction in FPGA design. No doubt this is because of the huge learning and legacy investment in testbenches. You don’t want to have to rework that – for any reason. UVM is widely supported and current so is becoming the standard of choice for verification methodology going forward.

That said, when an old-timer like me looks at the Cookbook (on-line, no-one uses paper books anymore) it can seem pretty overwhelming. Where do you start, and do you have to understand the whole thing before you can become effective? All that complexity is needed to handle the significantly higher complexity of verifying the systems we build today, but Tom told me not to panic. Most verification engineers don’t need to digest the whole thing. A few UVM experts will likely build the majority of the infrastructure most teams will need, leaving lesser mortals like me to assemble tests based on a much less demanding understanding of the standard. Following the cookbook metaphor, you can be a superchef and cook a 7-course gourmet meal from scratch if you choose, or you can go the BlueApron route, have most of the work already done for you (by your internal experts) and be able to throw together a great one-pot meal with minimal effort. Encouraging to hear that there’s a reasonably gentle learning curve for us beginners. Starting with, naturally a newly-added Basics section in the Cookbook.

What’s new in this version? Tom tells me of course it is fully updated to 1800.2 and especially all the examples are fully updated. They also archived all the OVM material that had been included in the earlier version – useful back then but largely unnecessary for today’s UVM users.

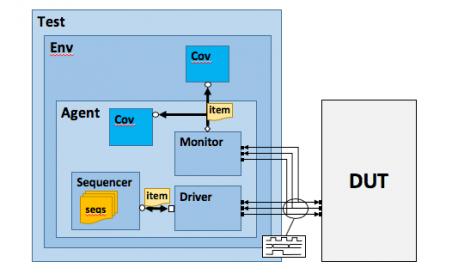

The main point he stressed for this update is a single recommended architecture to support emulation-friendly UVM testbenches. As emulation plays an increasingly important role in system verification, it becomes essential to ensure that testbenches can migrate with minimal change to emulator-based flows. To accomplish this, the Cookbook recommends split transactors communicating with the DUT through transaction methods rather pin-level driver/monitor components. If you are familiar with this approach, you’ll know one side of the transactor sits with the DUT (on the emulator) and the other side sits in the testbench. Transaction-level rather than signal-level data exchange allows the emulator run at faster speeds than would be possible if required to sync with the testbench on signal-level changes.

The Cookbook recommended methodology is closely aligned with the (open) UVM Framework and Questa VIP so you can spin-up quickly with a methodology that ensures your testbench development will be emulator-friendly. Tom mentioned a number of other improvements to the Cookbook, including (among others) updates to the Register Abstraction Layer reflecting changes in 1800.2, an updated UVM Connect chapter for those of you wanting to drive verification from higher-level TLM abstractions and a chapter consolidating information on messaging in UVM.

I won’t and can’t steal their thunder because there’s way too much to cover in a blog. Tom recommends that for those of you who are interested, you should register for their Webinar on September 11[SUP]th[/SUP] at 8am Pacific where I know you’ll get a much more expert summary of this update.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.