All semiconductor design work today rests on the three-legged stool of Foundries, EDA Tools and Designers. Close collaboration between the three make possible the successful completion of ever more complex designs, especially those at advanced nodes. Perhaps one of the most critical intersections of all three is during physical… Read More

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

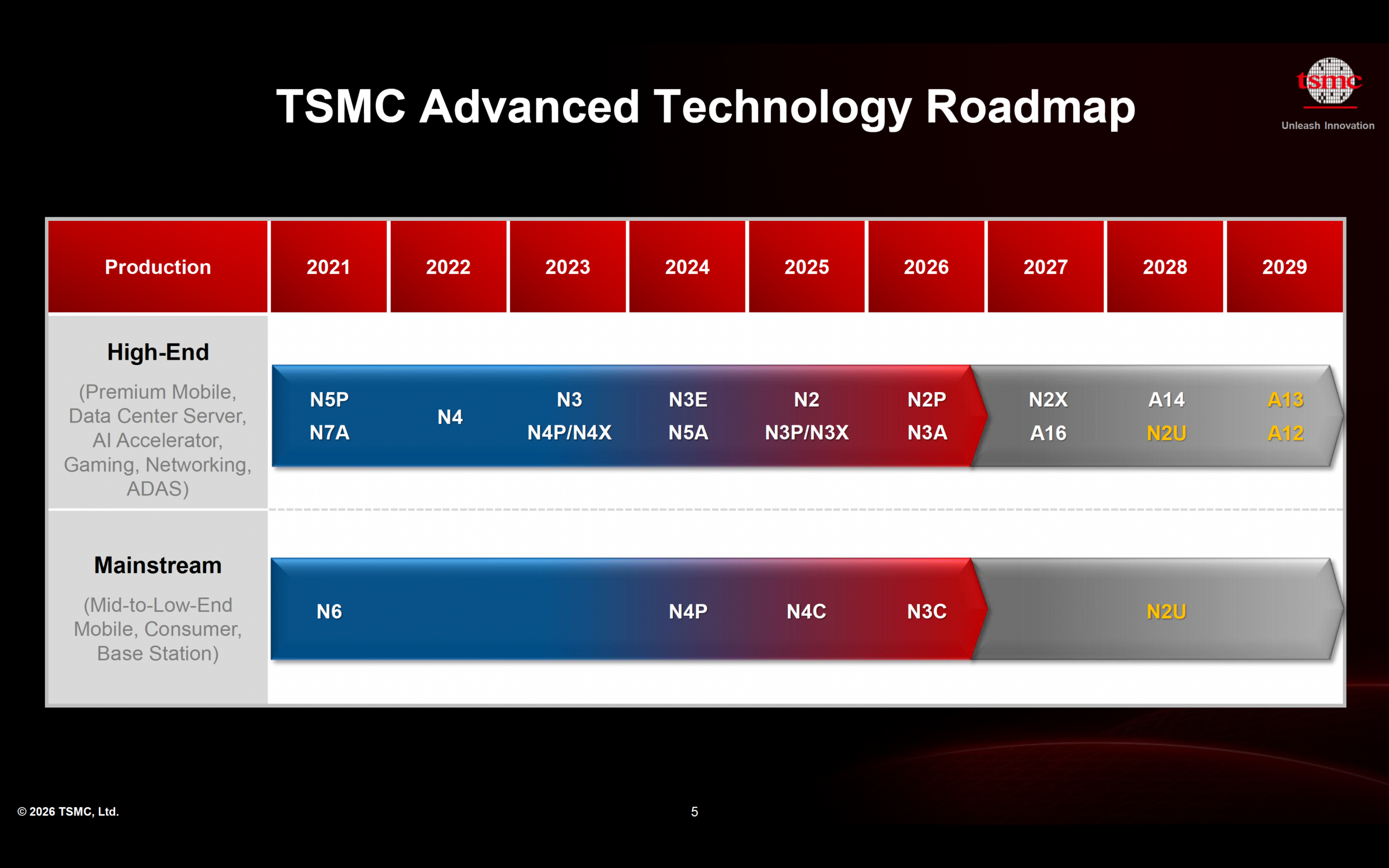

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More

The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

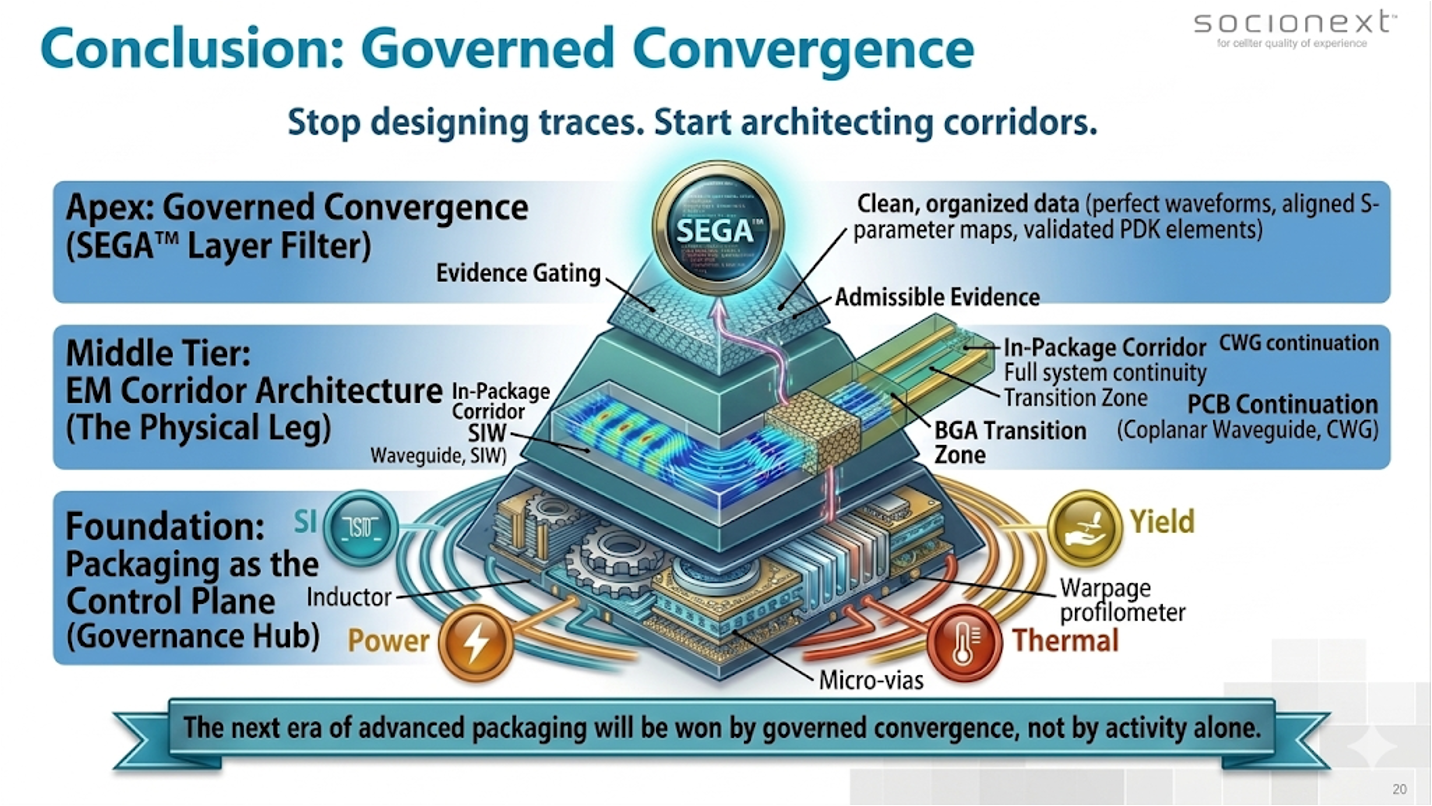

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read MoreIEDM 2020 Starts this Weekend

As I have discussed before, I believe that IEDM is the premier technical conference for understanding leading edge process technologies. Beginning this coming weekend, this year’s edition of IEDM will be held virtually, and I highly recommend attending.

The conference held a press briefing last Monday. The tutorial and short… Read More

Altair Expands Its Technology Footprint with I/O Profiling from Ellexus

Altair is a broad-based technology company with an ambitious vision. As stated on their website: Our comprehensive, open-architecture solutions for data analytics, computer-aided engineering, and high-performance computing (HPC), enable design and optimization for high performance, innovative, and sustainable products… Read More

Smoother MATLAB to HLS Flow

It hard to imagine design of a complex signal processing or computer vision application starting somewhere other than in MATLAB. Prove out the algorithm in MATLAB, then re-model in Simulink, to move closer to hardware. First probably an architectural model, using MATLAB library functions to prove out behavior of the larger system.… Read More

How Line Cuts Became Necessarily Separate Steps in Lithography

Pretty much all the semiconductor nodes in the last two decades have had at least one layer where the minimum pitch pushes the limitation of the state-of-the-art lithography tool, with a k1 factor < 0.5, i.e., the half-pitch is less than 0.5*wavelength/numerical aperture. A number of published reports [1-4] have touched upon… Read More

Verification IP proves essential for PCIe GEN5

PCI Express (PCIe) has become an important communication element in a wide range of systems. It is used to connect networking, storage, FPGA and GPGPU boards to servers and desktop systems. It has progressed a long way from its initial parallel bus format. Its evolution to a serial point to point configuration has been accompanied… Read More

The Practitioners View of DAC – Design, IP and Embedded

Next year will mark the 58th year for the Design Automation Conference. It’s hard to wrap your head around the fact this event dates back to 1964, when rock ‘n roll was new, cars were big and computers were even bigger. In its early days, the event was called the Design Automation Workshop. Pictured above is the cover of the very first… Read More

How Intel Stumbled: A Perspective from the Trenches

Bloomberg did an interview with my favorite semiconductor analyst Stacy Rasgon on “How the Number One U.S. Semiconductor Company Stumbled” that I found interesting. Coupled with the Q&A Bob Swan did at the Credit Suisse Annual Technology Conference I thought it would be good content for a viral blog.

Quantum Internet Explained

Building a quantum internet is a key ambition for many countries around the world, such a breakthrough will give them competitive advantage in a promising disruptive technology, and opens a new world of innovations and unlimited possibilities.

Recently the US Department of Energy (DoE) published the first blueprint of its… Read More

The Future of Connected Car Advertising

“Ads definitely work, but we can’t tell you how or why or give you any evidence,” – Tim Hwang, research fellow, Georgetown Center for Security and Emerging Technology

Two recent episodes of the Freakonomics Radio podcast tackle the question “Does advertising actually work?” and they coincided with a presentation… Read More

Solving the EDA tool fragmentation crisis