For those of you following the latest developments in electronic design it has become clear that the industry is transitioning through an inflection point that is shifting some of the ground rules of design. The increase in the speed and integration density in today’s systems are blurring the lines between chip design and system… Read More

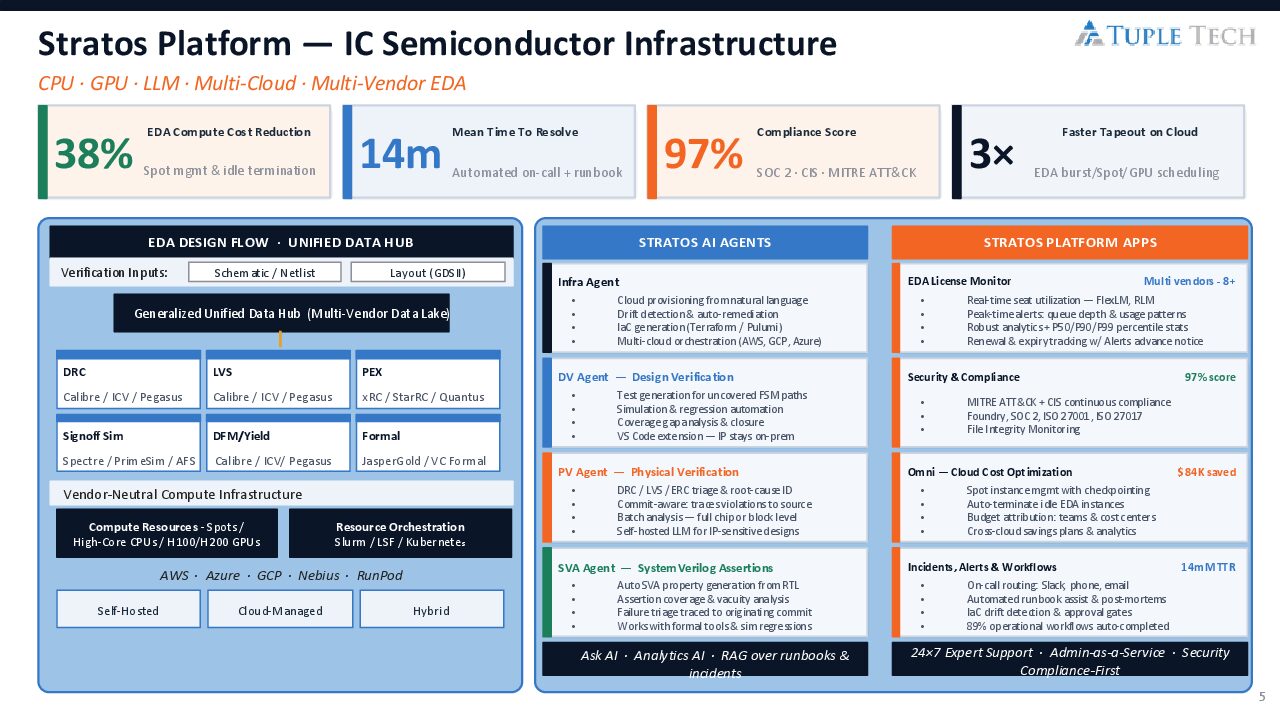

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreIoT and 5G Convergence

The Convergence of 5G and Internet of Things (IoT) is the next natural move for two advance technologies built to make users lives convenient, easier and more productive. But before talking about how they will unite we need to understand each of the two technologies.

Simply defined; 5G is the next-generation cellular network… Read More

Podcast EP36: Semiconductor Design Acceleration

Dan and Mike are joined by Michael Johnson (MJ), CTO at NetApp. MJ provides “behind the scene” insights into NetApp technology and how it has quietly revolutionized information storage and management for chip design. The key enabling technologies along with specific use cases are discussed. MJ also discusses moving… Read More

The Arm China Debacle and TSMC

Having spent 40 years in the semiconductor industry, many years working with Arm and even publishing the definitive history book “Mobile Unleashed: The Origin and Evolution of ARM Processors in Our Devices” plus having spent more than 20 years working with China based companies, I found the recent Arm China media circus quite … Read More

Why Optimizing 3DIC Designs Calls for a New Approach

The adoption of 3DIC architectures, while not new, is enjoying a surge in popularity as product developers look to their inherent advantages in performance, cost, and the ability to combine heterogeneous technologies and nodes into a single package. As designers struggle to find ways to scale with complexity and density limitations… Read More

Optimize AI Chips with Embedded Analytics

The foundry model, multi-source IP blocks, advanced packaging technologies, cloud computing, hyper-connectivity and access to open-source software have all contributed to the incredible electronics products of recent times. Along with this, the complexity of developing and taking a chip to market has also increased. And… Read More

Intel Architecture Day – Part 2: GPUs, IPUs, XeSS, OpenAPI

Introduction

At the recent Intel Architecture Day presentations, a breadth of roadmap plans were provided – an earlier article focused on the x86 client and data center cores and products. This article focuses on the GPU and IPU announcements.

Xe Graphics Core

The Intel GPU architecture for embedded, discrete, and data center… Read More

Intel Architecture Day – Part 1: CPUs

Introduction

The optimization of computing throughput, data security, power efficiency, and total cost of ownership is an effort that involves managing interdependencies between silicon and packaging technologies, architecture, and software. We often tend to focus on the technology, yet the architecture and software… Read More

AMS IC Designers need Full Tool Flows

Digital IC design gets a lot of attention, because all of our modern devices primarily use digital logic, but in reality whenever you have a sensor like a camera, accelerometer, gyroscope or any radio like Bluetooth, WiFi or NFC, then you’re really in the realm of analog, and that’s where mixed-signal IC design comes… Read More

Smoothing the Path to NoC Adoption

We’re creatures of habit. As technologists, we want to move fast and break things, but only on our terms. Everything else should remain the same or improve with minimum disruption. No fair breaking the way we do our jobs as we plot a path to greatness. This is irrational, of course. Real progress often demands essential changes where… Read More

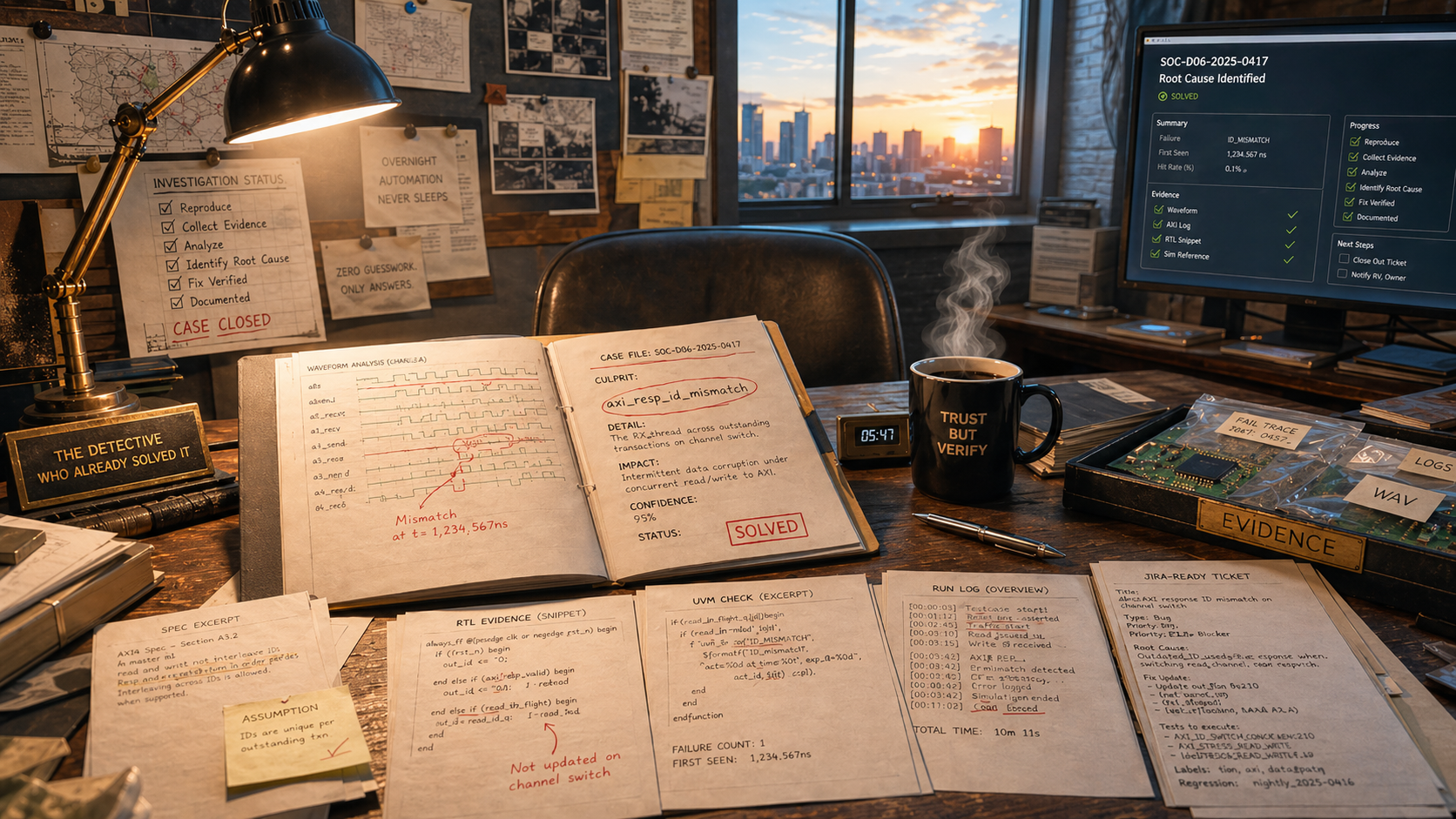

Solving the EDA tool fragmentation crisis