In a power hungry world of semiconductor devices, multiple ways are being devised to budget power from system to transistor level. The success of IoT (Internet of Things) Edge devices specifically depend on lowest power, lowest area, optimal performance, and lowest cost. These devices need to be highly energy efficient for sustained… Read More

Synopsys’ Andreas Kuehlmann on Software Development

Andreas Kuehlmann is the general manager of what is officially now known as the Software Integrity Group of Synopsys, what you might think of as Coverity although they have made some acquisitions too, so they now have a broader technology base. I sat down to talk to him last week.

He was brought up in Germany and came to the US in 1991 … Read More

Synopsys Buys Bluetooth IP

There is obviously a broad spectrum of semiconductor IP but broadly speaking it seems to fall into three buckets:

- foundation IP: standard cells, memories

- microprocessors and associated peripherals

- interface IP

Foundation IP is where it all started. When I was at Compass Design Automation in the 1990s that was pretty much what… Read More

Antun Domic, on Synopsys’ Secret Sauce in Design

Antun Domic is the GM of the Design Group at Synopsys. I sat down with him a couple of weeks ago.

His name is Croatian although, of course, there was no Croatia back then it was part of Yugoslavia. But in fact he grew up in Chile and went to university there where he studied EE and math. He came to the US as a grad student and did a PhD at MIT in … Read More

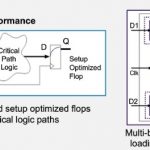

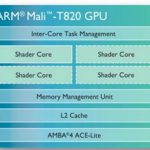

How ARM Implemented a Mali GPU using Logic Synthesis and Place/Route Tools

ARM is a well-known semiconductor IP provider and they often create a reference design so that SoC companies can have a starting point to work with. On the GPU side of IP the ARM engineers have an architecture called Mali, and a recent webinar hosted by Synopsys reviewed how the physical design area was minimized by using a combination… Read More

Circuit Simulation Update from #52DAC

Actual users of circuit simulators told their design and simulation stories at DAC during a luncheon sponsored by Synopsys on June 8th. I always prefer to hear from a design engineer versus a marketing person about what tool they use for circuit simulation, and how it helps them analyze their design goals. This year there were engineers… Read More

Why Automotive IP Portfolio is not just IP

Synopsys is launching a broad IP portfolio to support SoC development dedicated to emerging automotive complexes functions, like Driver Assistance (ADAS), Driver Information, Vehicle Network or Infotainment. I was never involved into IC design for Automotive, but I have designed ASIC for avionics (CFM56 motor control) or… Read More

Synopsys Aquires Security IP Company Elliptic

On Monday Synopsys announced that it was acquiring Elliptic Technologies. They have one of the largest portfolios of security IP consisting of both semiconductor IP blocks and software. Increasingly, security requires a multi-layer approach involving both secure blocks on the chip and a software stack on top of that.

Elliptic’s… Read More

Synopsy Eats Their Own Dogfood

One of the most interesting presentations that I went to was the last presentation at the Synopsys Custom Lunch (no, the lunch wasn’t custom, we all got the same, but the presentations were about custom design). Since the last presentation was by Synopsys themselves and not by a customer, it wouldn’t seem promising that it could … Read More

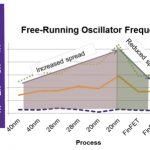

Synopsys Vision on Custom Automation with FinFET

In an overwhelmingly digital world, there is a constant cry about the analog design process being slow, not automated, going at its own pace in the same old fashion, and so on. And, the analog world is not happy with the way it’s getting dragged into imperfect automation so it can be more like the digital world. True, the analog world… Read More