The trend is clear, AI and HPC is moving to chiplet-based, or heterogenous design to achieve the highest levels of performance, while traditional monolithic system-on-chip (SoC) designs struggle to scale. What is also clear is the road to this new design style is not a smooth one. There are many challenges to overcome. Some are … Read More

Design-Technology Co-Optimization (DTCO) Accelerates Market Readiness of Angstrom-Scale Process Technologies

Design-Technology Co-Optimization (DTCO) has been a foundational concept in semiconductor engineering for years. So, when Synopsys referenced DTCO in their April 2025 press release about enabling Angstrom-scale chip designs on Intel’s 18A and 18A-P process technologies, it may have sounded familiar—almost expected. … Read More

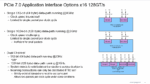

WEBINAR: PCIe 7.0? Understanding Why Now Is the Time to Transition

PCIe is familiar to legions of PC users as a high-performance enabler for expansion slots, especially GPU-based graphics cards and M.2 SSDs. It connects higher-bandwidth networking adapters and niche applications like system expansion chassis in server environments. Each PCIe specification generation has provided a leap… Read More

The Road to Innovation with Synopsys 224G PHY IP From Silicon to Scale: Synopsys 224G PHY Enables Next Gen Scaling Networks

The explosive growth of large language models (LLMs) has created substantial new requirements for chip-to-chip interconnects. These very large models are trained in high-performance data centers. Multiple accelerators need to work seamlessly to make all this possible as the bandwidth between accelerators directly impacts… Read More

Webinar – Achieving Seamless 1.6 Tbps Interoperability with Samtec and Synopsys

It is well-known that AI is upending conventional wisdom for system design. Workload-specific processor configurations are growing at an exponential rate. Along with this is an exponential growth in data bandwidth needs, creating an urgency for 1.6T Ethernet. A recent SemiWiki webinar dove into these issues. Synopsys and … Read More

SNUG 2025: A Watershed Moment for EDA – Part 2

At this year’s SNUG (Synopsys Users Group) conference, Richard Ho, Head of Hardware, OpenAI, delivered the second keynote, titled “Scaling Compute for the Age of Intelligence.” In his presentation, Richard guided the audience through the transformative trends and implications of the intelligence era now unfolding before… Read More

Automotive Functional Safety (FuSa) Challenges

Modern vehicles have become quite sophisticated, like a supercomputer on wheels. They integrate a vast number of electronic components, including thousands of chips, to deliver advanced functionalities ranging from infotainment to critical safety systems. This increasing complexity necessitates a robust approach to … Read More

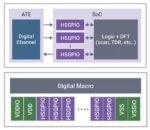

Scaling AI Infrastructure with Next-Gen Interconnects

At the recent IPSoC Conference in Silicon Valley, Aparna Tarde gave a talk on the importance of Next-Gen Interconnects to scale AI infrastructure. Aparna is a Sr. Technical Product Manager at Synopsys. A synthesis of the salient points from her talk follows.

The rapid advancement of artificial intelligence (AI) is fundamentally… Read More

The Growing Importance of PVT Monitoring for Silicon Lifecycle Management

In an era defined by complex chip architectures, ever-shrinking technology nodes and very demanding applications, Silicon Lifecycle Management (SLM) has become a foundational strategy for optimizing performance, reliability, and efficiency across the lifespan of a semiconductor device. Central to effective SLM are Process,… Read More

Achieving Seamless 1.6 Tbps Interoperability for High BW HPC AI/ML SoCs: A Technical Webinar with Samtec and Synopsys

HPC Bandwidth Explosion and 1.6T Ecosystem Interop Need

The exponential growth in data bandwidth requirements driven by HPC systems, AI, and ML applications has set the stage for an ever-increasing need for 1.6Tbps Ethernet. As data centers strive to manage vast data transfers with maximum efficiency, the urgency for interoperability… Read More