In the fast-paced semiconductor industry Synopsys has redefined EDA with its Synopsys.ai Copilot, a generative AI tool. Since its launch in November 2023, and yes I was at the launch and very skeptical, Copilot has evolved to address the industry’s growing design complexity and projected 15-30% workforce gap by 2030. Let’s… Read More

The Rise, Fall, and Rebirth of In-Circuit Emulation (Part 1 of 2)

Introduction: The Historical Roots of Hardware-Assisted Verification

The relentless pace of semiconductor innovation continues to follow an unstoppable trend: the exponential growth of transistor density within a given silicon area. This abundance of available semiconductor fabric has fueled the creativity of design… Read More

eBook on Mastering AI Chip Complexity: Pathways to First-Pass Silicon Success

The rapid evolution of artificial intelligence (AI) is transforming industries, from autonomous vehicles to data centers, demanding unprecedented computational power and efficiency. As highlighted in Synopsys’ guide, the global AI chip market is projected to reach $383 billion by 2032, growing at a 38% CAGR. This … Read More

Synopsys Enables AI Advances with UALink

The evolution of hyperscale data center infrastructure to support the processing of trillions of parameters for large language models has created some rather substantial design challenges. These massive processing facilities must scale to hundreds of thousands of accelerators with highly efficient and fast connections.… Read More

448G: Ready or not, here it comes!

The march toward higher-speed networking continues to be guided by the same core objectives as has always been : increase data rates, lower latency, improve reliability, reduce power consumption, and maintain or extend reach while controlling cost. For the next generation of high-speed interconnects, these requirements … Read More

Synopsys Webinar – Enabling Multi-Die Design with Intel

As we all know, the age of multi-die design has arrived. And along with it many new design challenges. There is a lot of material discussing the obstacles to achieve more mainstream access to this design architecture, and some good strategies to conquer those obstacles. Synopsys recently published a webinar that took this discussion… Read More

Synopsys FlexEDA: Revolutionizing Chip Design with Cloud and Pay-Per-Use

On July 9, 2025, Vikram Bhatia, head of product management for Synopsys’ cloud platform, and Sashi Obilisetty, his R&D engineering counterpart, presented a DACtv session on Synopsys FlexEDA, as seen in the YouTube video. Drawing from three and a half years of data, the session showcased how this cloud-based, pay-per-use… Read More

cHBM for AI: Capabilities, Challenges, and Opportunities

AI’s exponential growth is transforming semiconductor design—and memory is now as critical as compute. Multi-die architecture has emerged as the new frontier, and custom High Bandwidth Memory (cHBM) is fast becoming a cornerstone in this evolution. In a panel session at the Synopsys Executive Forum, leaders from AWS, Marvell,… Read More

Podcast EP299: The Current and Future Capabilities of Static Verification at Synopsys with Rimpy Chugh

Dan is joined by Rimpy Chugh, a Principal Product Manager at Synopsys with 14 years of varied experience in EDA and functional verification. Prior to joining Synopsys, Rimpy held field applications and verification engineering positions at Mentor Graphics, Cadence and HCL Technologies.

Dan explores the expanding role of static… Read More

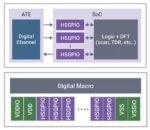

Synopsys Addresses the Test Barrier for Heterogeneous Integration

The trend is clear, AI and HPC is moving to chiplet-based, or heterogenous design to achieve the highest levels of performance, while traditional monolithic system-on-chip (SoC) designs struggle to scale. What is also clear is the road to this new design style is not a smooth one. There are many challenges to overcome. Some are … Read More