PCB designers can perform pre-route simulations, follow layout and routing rules, hope for the best from their prototype fab, and yet design errors cause respins which delays the project schedule. Just because post-route analysis is time consuming doesn’t mean that it should be avoided. Serial links are found in many PCB designs,… Read More

Fault Sim on Multi-Core Arm Platform in China. Innovation in VerificationHow much can running on a multi-core (Arm)…Read More

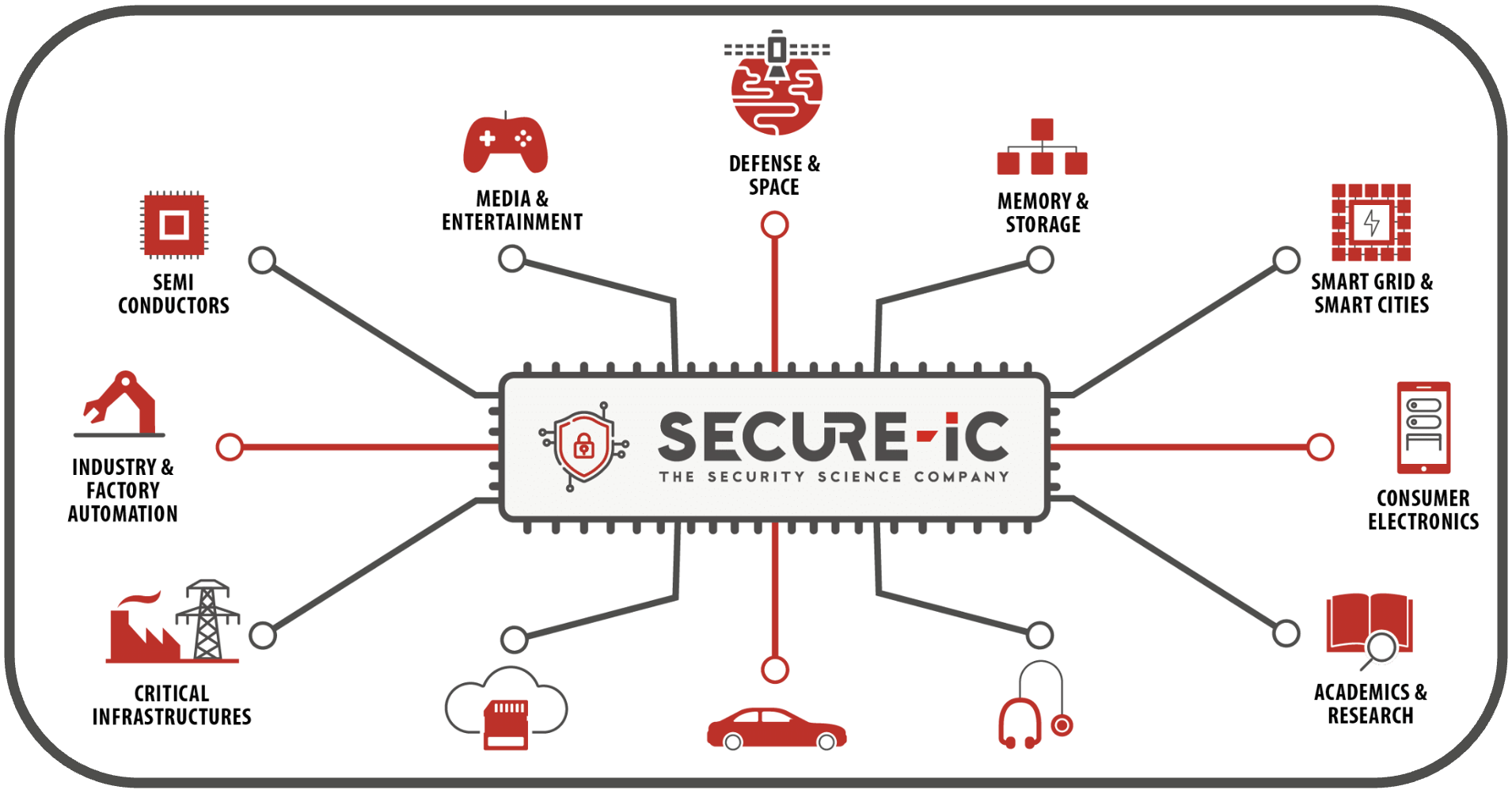

Fault Sim on Multi-Core Arm Platform in China. Innovation in VerificationHow much can running on a multi-core (Arm)…Read More How Secure-IC is Making the Cyber World a Safer PlaceSecuring the data and all the associated transactions…Read More

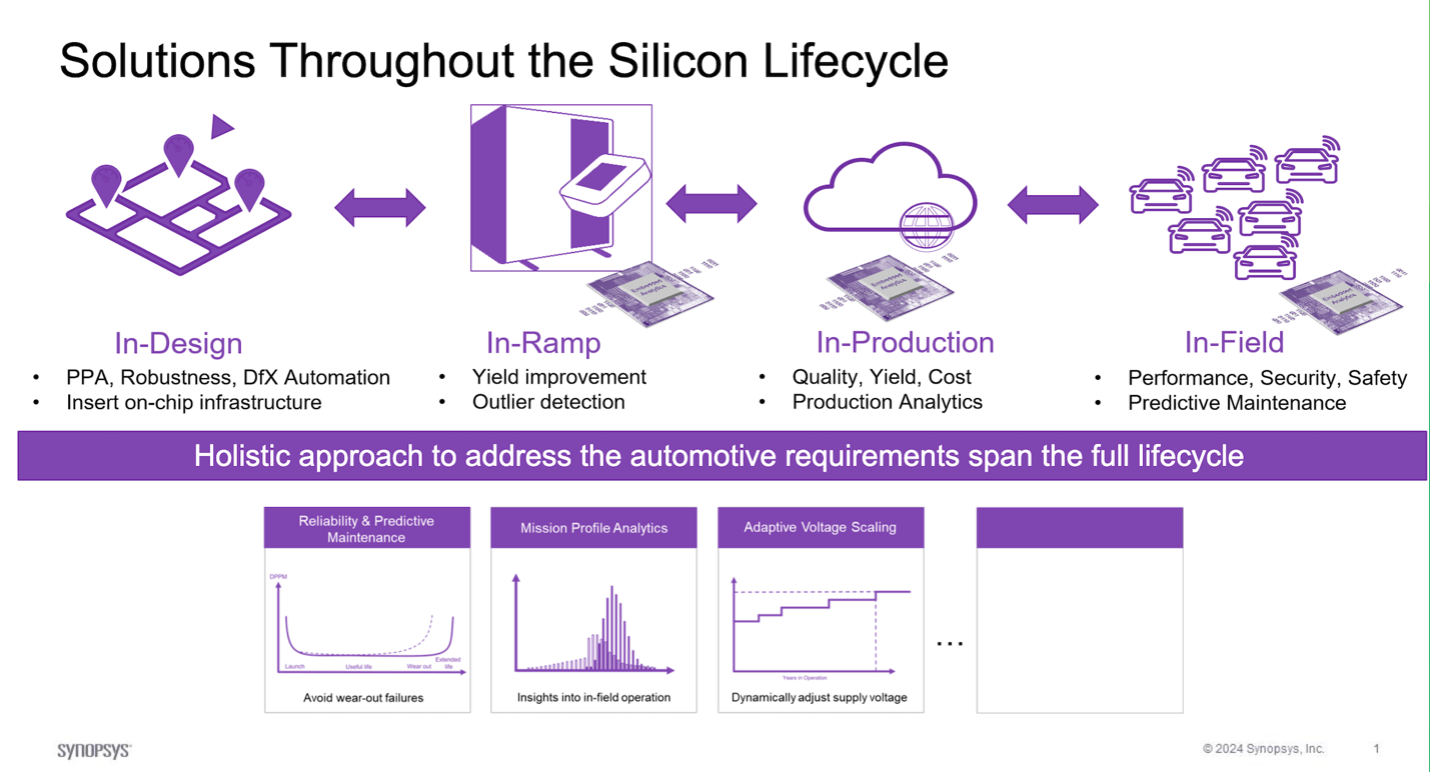

How Secure-IC is Making the Cyber World a Safer PlaceSecuring the data and all the associated transactions…Read More Lifecycle Management, FuSa, Reliability and More for Automotive ElectronicsSynopsys recently hosted an information rich-webinar, modestly titled…Read More

Lifecycle Management, FuSa, Reliability and More for Automotive ElectronicsSynopsys recently hosted an information rich-webinar, modestly titled…Read MoreEnabling Imagination: Siemens’ Integrated Approach to System Design

In today’s rapidly advancing technological landscape, semiconductors are at the heart of innovation across diverse industries such as automotive, healthcare, telecommunications, and consumer electronics. As a leader in technology and engineering, Siemens plays a pivotal role in empowering the next generation … Read More

Ceva Accelerates IoT and Smart Edge AI with a New Wireless Platform IP Family

Ceva is a very focused company. In its words, the leader in innovative silicon and software IP solutions that enable smart edge products to connect, sense, and infer data more reliably and efficiently. You can see some of its accomplishments here. The company has been licensing IP for more than twenty years with more than 17 billion… Read More

LRCX- Mediocre, flattish, long, U shaped bottom- No recovery in sight yet-2025?

– Lam reports another flat quarter & guide- No recovery in sight yet

– Seems like no expectation of recovery until 2025- Mixed results

– DRAM good- NAND weak- Foundry/Logic mixed-Mature weakening

– Clearly disappointing to investors & stock hoping for a chip recovery

Another Flat Quarter &

… Read MoreWEBINAR: The Rise of the DPU

The server and enterprise network boundary has seen complexity explode in recent years. What used to be a simple TCP/IP offload task for network interface cards (NICs) is transforming into full-blown network acceleration using a data processing unit (DPU), able to make decisions based on traffic routes, message content, and… Read More

Podcast EP220: The Impact IQE’s Compound Semiconductors Are Having on the Industry with Dr. Rodney Pelzel

Dan is joined by Dr. Rodney Pelzel, he has over 20 years of experience in the semiconductor industry, with deep expertise in semiconductor materials engineering and the epitaxial growth of compound semiconductors. Dr. Pelzel joined IQE as a Production Engineer in 2000 and is now head of R&D and is tasked with creating unique… Read More

CEO Interview with Clay Johnson of CacheQ Systems

Clay Johnson has decades of executive experience in computing, FPGAs and development flows, including serving as vice president of the Xilinx (now AMD) Spartan Business Unit. He has a vision to enable the next phase of computing.

Tell us about CacheQ.

CacheQ is a little over six years old and we have about 10 people. We focus on application… Read More

Alphawave Semi Bridges from Theory to Reality in Chiplet-Based AI

GenAI, the most talked-about manifestation of AI these days, imposes two tough constraints on a hardware platform. First, it demands massive memory to serve large language model with billions of parameters. Feasible in principle for a processor plus big DRAM off-chip and perhaps for some inference applications but too slow … Read More

Design Stage Verification Gives a Boost for IP Designers

The concept of shift left is getting to be quite well-known. The strategy involves integrating various checks typically performed later in the design process into earlier stages. The main benefit is to catch and correct defects or errors at an earlier stage when it’s easier and faster to address. For complex SoC design, … Read More

Intel High NA Adoption

On Friday April 12th Intel held a press briefing on their adoption of High NA EUV with Intel fellow and director of lithography Mark Phillips.

In 1976 Intel built Fab 4 in Oregon, the first Intel fab outside of California. With the introduction of 300mm Oregon became the only development site for Intel with large manufacturing, development,… Read More

Intel High NA Adoption