Image sensors are all around us with the cell phone being a popular example, and 35mm DSLR camera being another one. Last week I spoke with Kenton Veeder, an engineer at Senseeker that started his own image sensor IP and consulting services company. Instead of focusing on the consumer market, Kenton’s company does sensor design work for the military and scientific markets.

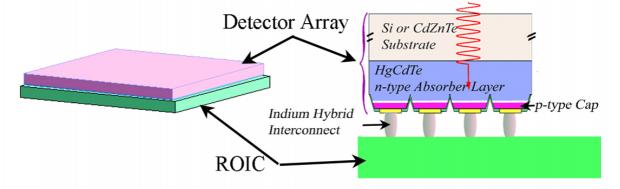

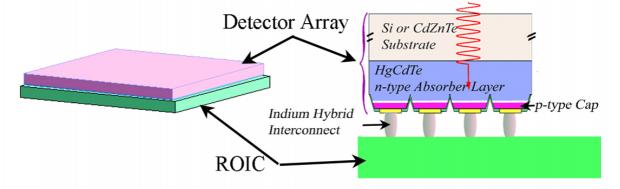

Read Out Integrated Circuit (ROIC)

Interview Questions

Q: When did you get started in IC design?

A: I graduated in 2001 from Texas A&M, then worked at Raytheon doing image sensor design in So Cal, now called Raytheon Vision Systems. I earned a Masters degree in AMS IC design, and at the university we did chip designs.

Kenton Veeder, Founder of Senseeker

Q: What did you work on after Raytheon?

A: In 2008 I went to work at a Boston-based start-up called SiOnyxand started using Tanner EDA tools like L-Edit for designing new photonic devices.

Q: When did you start-up Senseeker?

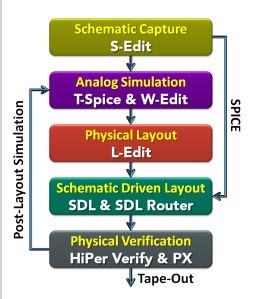

A: We returned to Santa Barabara in 2009 and then I started my IP and consulting business. Sunseeker engineering was founded on 9/9/9. We design complex digital image sensors and use most of the Tanner EDA tools:

- Schematic capture with S-Edit

- Circuit simulation with T-Spice

- IC layout with L-Edit

- DRC and LVS with HiPer Verify

- Verilog-A for modeling

Q: How large is Senseeker?

A: It’s two of us working together as a team. Both of us are mixed-signal IC designers. I’m specialized in D to A converters for image sensors, my coworker does the rest. Both of us are front-to-back designers, doing both schematics, layout and simulation.

The IC layout itself plays a huge role in image sensor design.

Q: Who are your customers?

A: My customers are in aerospace and scientific community, using the infra-red light spectrum. In commercial sensors you would integrate the detector with each pixel, however for infra-red we use almost a 3D stack with a silicon detector on top of a CMOS pixel array. The IR community calls it a Read Out Integrated Circuit (ROIC), and they are used by DOD companies.

Q: Have you published about your IC design?

A: Yes, we’ve published in controlled environments, however we cannot publicly show the details of our work.

Q: What does Senskker provide?

A: We provide IP and design services, and all of our customers are DOD-based. These Hybrid image sensors have been done for much longer than the CMOS image sensors for cell phones and DSLR.

Q: What is the size of the image sensors you design?

A: Hybrid sensors are on the order of 50 mega-pixels to 64 mega-pixels, the IR sensors ted to be limited by a minimum pixel size. Larger pixel sizes are needed to keep sensitivity, about a 20um pixel size is required for IR. These sensors are so large that you may have just 2 sensors per wafer. The physics of the wavelength of light are the limiting factor.

Q: Which process nodes are you designing with?

A: Our sensor designs use from the 90nm to 350nm nodes. The processes range from bulk CMOS to Radhard, to SOI. Quantities are much lower than for the consumer market. Space-based applications require rad-hard processes and some of the Military designs require rad-hard. SOI can also deliver better noise characteristics than bulk CMOS, however most of our design is done with bulk CMOS.

Q: Which foundries are you using?

A: We are using foundries like: On Semi, TowerJazz, IBM.

Q: Are there micro-lenses on top of the image sensors?

A: Yes, we partner with sensor chip assemblers that place the detectors on top of the image sensor, which may have micro-lenses and use Indium bumps.

Q: How do you approach image sensor designs, from the top-down or bottom up?

A: It all depends. We can use Matlab for systems-level modeling, then also do bottom-up IC layout. We are doing parallel top-down and bottom-up design. Often it’s pixel outward design.

Q: What languages do you use for simulation?

A: We’re doing extensive Verilog-A modeling, plus Verilog as needed for digital, then also create noise models in MathCad. Some use of simulink with Matlab. Mostly we’re using Verilog-A and SPICE simulated in Tanner EDA tools. The SMASH simulator from Dolphin is also used.

I’ve written Verilog-A descriptions of gates to speed up AMS simulation run times. We simulate a small core sensor that needs to simulate for multiple milliseconds, where we are looking at multiple rows and columns of our sensor.

Q: How does your IP get debugged?

A: When an IP customer gets first silicon then we come and help debug the new devices. We create a set of tests for each mode and feature of the sensor.

Q: How long are your IC design projects?

A: A typical consulting service engagement goes from 2.5 months to 8 months from contract to delivery.

Q: Which version of Tanner EDA tools are you using now?

A: We are using 15.2.3 for projects now, and we also did the beta on v16 because of OA. Our customers use Cadence so having OA in Tanner EDA makes the IC design flow very easy for us. Our large image sensor designs need a good, hierarchical database like OA, so that will help manage the process better.

Q: What type of computers are you using?

A: The hardware are over-clocked workstations, liquid-cooled, running at 4GHz. These computers run Windows 7.

Q: How long do your IC simulations run?

A: Our simulations can run up to 10 days or so, using both SPICE and Verilog-A models.

Q: How is the support from Tanner EDA?

A: I’m quite happy with Tanner EDA support, they’ve been very helpful, show us how to get the best simulation results. I’ve enjoyed using the Tanner tools over the years, even in comparison to EDA tools from Cadence and Mentor.

Q: What could be improved with the Tanner tools?

A: HiPer Verify is pretty good at reading in Calibre rule decks, although it’s not as quick on verifying large repetitive circuits.

Summary

Senseeker Engineering has designed digital image sensors for the IR market using a mixture of EDA tools from Tanner EDA, Dolphin Integration and MathWorks. The v16 release of Tanner EDA tools supports the OA database from Cadence, allowing Tanner designs to be easily used in a Cadence tool flow. Read the press release about v16 to see all of the new features added.

Comments

There are no comments yet.

You must register or log in to view/post comments.