The entire field of Artificial Intelligence (AI) has resulted from what is called “first principles thinking”, where problems are re-examined using a complete reassessment of the underlying issues and potential solutions. It is a testament to how effective this can be that AI is being used for a rapidly expanding number of applications that previously challenged or defied traditional approaches in programming. Even using conventional CPU based architectures AI offers enormous advantages over conventional sequential “instruction based” coding in a wide range of fields, including autonomous driving, sensor data analysis, resource optimization, IoT, safety systems, etc. Yet even more impressive improvements in AI performance have come from the use of optimized AI processors.

Some of these AI processors rely on several well understood concepts that can improve the efficiency of the types of computations made in a neural network. Adding parallelism is the first approach, the other is to move memory closer to the processing elements. The AI chip company Mythic is making AI accelerator chips that use these proven methods and adds to them with an ingenious new “first principles” approach.

The seed for their idea is that in Ohm’s law V=IR is multiplication. The multiply-accumulate (MAC) operation is the mainstay of AI neural network implementation. Digital multiplication is cumbersome, and frequently inefficient and slow, even if reduced to 8-bit precision which – works well enough for many recognition and inference tasks.

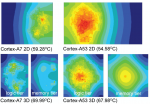

Mythic has introduced analog computation as the method for performing MAC by using Flash memory cells as precision resistors to hold training coefficients. When voltage values are run through the flash memory cells the output current is the result of an analog computation. Using the memory cell as a computation unit saves not only memory access, but also significantly reduces computation time.

However, this requires significant analog design expertise, especially in designing memory cells and analog to digital converters. Accuracy is essential and it is extremely important to ensure that the entire computation is performed accurately.

Because this is a mixed signal design, SPICE simulation alone is not adequate for verification. Mixed signal simulation is called for. Mentor, a Siemens business and Mythic just made an announcement about Mythic’s use of Mentor’s Analog FastSPICE (AFS) and Symphony mixed signal simulation platform to simulate and verify the thousands of ADCs that are needed in their designs, and to verify overall chip performance. This involves RTL simulation along with the analog simulation.

Mythic chose Mentor’s Analog FastSPICE because of its proven speed and accuracy at nanometer-scale. It has demonstrated excellent correlation with silicon when performing full spectrum device noise analysis. The Symphony mixed signal simulation platform helps to verify the integration of digital and analog logic in their Intelligence Processing Units (IPUs). Mythic say they have been very pleased with the intuitive use model, powerful debugging features and configuration support.

The development of electronic systems is a layered process involving a chain of steps vital for reaching success. First principles are not only being used in the last step of chip design, they were applied by Mentor as well in the development of their enabling solutions. It’s conceivable that if Mythic wanted to apply their innovative approach and the needed supporting tools were not available, they might not have had the technical success they are enjoying today. The full announcement of Mythic’s use of Mentor’s analog and mixed signal solutions is available on the Mentor Website.