SPI, invented some four decades ago, is so successful as a low-pin-count interface for microcontrollers and processor cores that it spurred memory makers to incorporate both the physical signaling interface and advanced memory command protocols into serial flash and serial pseudo-SRAM (PSRAM) devices. Those protocols, however, fractured into manufacturer-specific versions. A few years ago, JEDEC expanded SPI into xSPI, aiming to gather the most popular proprietary over-SPI serial memory protocol variants into a single superset standard. Now that xSPI adoption is widespread across the industry, CAST’s xSPI-MC IP core is an attractive offering that blends a protocol engine and a serial memory controller in functional safety-ready configurations that are fully synthesizable and suitable for practically any serial flash or serial PSRAM application.

From four wires to plug & play auto-configuration

The power of SPI lies in its ability to communicate with a wide range of attached peripherals, including sensors, displays, control devices, and, of course, serial memory. A basic SPI implementation has four lines: a serial clock, a slave select, master-out-slave-in (MOSI, serial data output by a master), and master-in-slave-out (MISO, serial data output by a slave).

Early implementations simply connected the pins and relied on software to manage transfers on a per-device basis. Eventually, to speed up software development, manufacturers created over-SPI protocols with device command sets that offered some consistency as long as designers were loyal to that manufacturer.

Without firm guidelines, for instance, bit widths and clock rates (which are theoretically not limited, but in practice, signal integrity starts having an effect around 20 MHz), the over-SPI protocols diverged at the whim of manufacturers. While specifics differ, the general form of an over-SPI protocol resembles this:

One command structure is standardized: obtaining the device ID. A master sends a 9Fh to request a device ID, and a device responds with its unique JEDEC-registered ID. That implies a master can maintain a table of supported device IDs and their corresponding protocols, query the attached device, and initiate transfers using the correct commands and parameters.

xSPI defines just such an auto-configuration method for serial memory devices by tabulating support for various over-SPI protocols, selectable by device ID. The same scheme allows adding other over-SPI protocols to a controller, as long as the device IDs are unique.

A quick look at the CAST xSPI-MC IP core

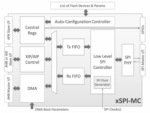

It’s also possible to configure wider interfaces to speed up transfers while still keeping pin counts relatively low using the same scheme. CAST leverages this capability in the xSPI-MC IP core, supporting xSPI, HyperBus (a 12-pin interface originally designed by Cypress), and Xccela (a 12-pin interface created by Micron). Both specifications fall into the octal SPI category with eight data lines tuned for higher-frequency operation. The xSPI-MC SPI controller and PHY scale across single-, dual-, quad-, octal-, and 16x SPI buses.

Run-time configurability enables users to detect a variety of devices. The configuration can be done with zero software overhead to initialize the controller and a memory device, or it can be modified in software. The device ID table is stored off-core, for instance, in ROM or OTP memory so that it can be updated easily. This configurability can be a project-saver – it’s not uncommon to get near the end of a design and discover, for supply chain or pricing reasons, the memory device has to switch to a different part.

The PHY is of particular interest – it’s a soft PHY specifically designed for SPI, implementing only the logic required for the interface with no excess, so it takes considerably less area. Unlike hard PHYs, which typically require qualification in a specific process node, CAST implemented the xSPI-MC soft PHY in fully synthesizable RTL, ready for any foundry, process node, or standard-cell library. This soft PHY also integrates into a standard ASIC or FPGA flow with no analog bring-up procedures, and it can drop directly into FPGA-based prototyping platforms for a smooth design workflow. These soft PHY attributes open up more implementation options, eliminate foundry dependencies, and make designs highly portable, reducing schedule risk.

Use cases include firmware, data, parameter, and log storage

xSPI-MC use cases span a range of application segments for serial flash and serial PSRAM:

- With automotive applications, a popular use case, the xSPI-MC supports nine ISO 26262-ready core configurations, ranging from ASIL-B to ASIL-D levels. Enhancements such as spatial redundancy and CRC protection enable swifter functional safety (FuSa) certification. Engine control units with firmware storage and XIP boot, displays that store navigation, audio, or user interface data, and EV battery management systems with calibration tables and fault log storage are a few use-case examples.

- In IoT and edge devices, sensor nodes with firmware and configuration parameters are a common use case. The onset of AI also requires storage of model weights, and wireless communication nodes can store upgradable protocols.

- Industrial automation controllers often have firmware storage. Robotics platforms also need real-time parameter tables and event logging, while smart meters require non-volatile event and usage logging.

- Consumer electronics often feature OTA (over-the-air) firmware updating. Small displays may use serial PSRAM for framebuffers and rendering. Earbuds and hearing aids present an ultra-small form factor, and the space saved by the soft PHY can make a difference. Gaming controllers and handheld consoles also need configuration and save-state storage.

xSPI-MC IP core flexibility also includes Verilog parameters that enable feature selection, reset value definition, AHB bus configuration, and SPI controller configuration. More info on the xSPI-MC IP core and its applications is available on the CAST website:

xSPI-MC: xSPI, HyperBus™, & Xccela™ Serial Memory Controller