Design IP revenues had achieved $6.67B in 2022, after $5.56B in 2021, or 20.2% growth after 19.4% in 2021 and 16.7% in 2020. IPnest has released the “Design IP Report” in April 2023, ranking IP vendors by category (CPU, DSP, GPU & ISP, Wired Interface, SRAM Memory Compiler, Flash Memory Compiler, Library and I/O, AMS, Wireless Interface, Infrastructure and Misc. Digital) and by nature (License and Royalty).

The main trends shaking the Design IP in 2022 are very positive for most of the IP vendors, especially for 4 of the Top 5: ARM, Synopsys, Imagination and Alphawave growing by more than the market, respectively 24.5%, 22.1%, 23.1% and 94.7%. Rambus and Alphawave benefit from their recent IP vendor acquisition, PLDA, AnalogX and Hardent for the first, OpenFive for Alphawave, but their organic growth was already great. In summary, the Top 10 IP vendors have grown by 24.6%, when all others by 5.3%, this can be seen as an effect of consolidation, as a Top vendor will make proportionally more design win than “others”.

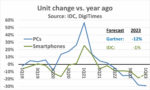

Synopsys, Alphawave and Rambus growth confirm again in 2022 the importance of the wired interface IP category (with 26.8% growth) aligned with the data-centric application, hyperscalar, datacenter, networking or AI. But the good performance of ARM and IMG proves the come back of the smartphone industry and the emergence of automotive as new growth vector for Design IP.

Looking at the 2016-2022 IP market evolution can bring interesting information about the main trends. Global IP market has grown by 94.8% when Top 3 vendors have seen unequal growth. The #1 ARM grew by 66.5% when the #2 Synopsys grew by 194% and Cadence (#3) by 203%. Market share information is even more significant. ARM move from 48.1% in 2016 to 41% in 2022 when Synopsys enjoy a move from 13.1% to 22% and Cadence is passing from 3.4% to 5.4%.

This can be synthetized with the comparison of 2016 to 2022 CAGR:

- ARM CAGR 8.9%

- Synopsys CAGR 19.7%

- Cadence CAGR 20.3%

When the global IP market has seen 2016 to 2022 CAGR of 11.8%.

The strong information is that the Design IP market has enjoyed 11.8% CAGR for 2016-2022! Zooming on the categories (Processor, wired Interface, Physical, Digital), market share 2017 to 2022 evolution clearly shows interface category growth (18% to 24.9%) at the expense of processor (CPU, DSP, GPU) declining from 57.6% to 49.5%. When Physical and Digital are almost stable, as it can be seen on the above picture.

Being very synthetic, Design IP markey is split in quarter:

- Processor (CPU, DSP, GPU) weigth one half (two quarter)

- Wired Interface weight one quarter

- Digital and Physical one quarter in total

IPnest has also calculated IP vendors ranking by License and royalty IP revenues:

Synopsys is the clear #1 by IP license revenues with 29.7% market share in 2022, when ARM is #2 with 25.2%. Alphawave, created in 2017, is now ranked #4 just behind Cadence, showing how high performance SerDes IP is essential for modern data-centric application (Alphawave is leader for PAM4 112G SerDes available in 7nm, 5nm and 3nm from various foundries, TSMC, Samsung and Intel-IFS). Analyze written last year stay valid!

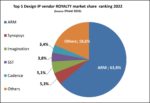

The 2022 ranking for Royalty shows ARM’s dominance with 63.8% market share, not a surprise if we consider their customer installed base and their strong position in the smartphone industry. Imagination Technologies (IMG) position of #3 is consistent. Interesting to notice, both companies are expected to IPO in 2023…

With 20% YoY growth in 2021 and 2022, the Design IP industry is simply confirming how incredibly healthy is this niche within the semiconductor market and the past 2016 to 2022 CAGR of 11.8% is a good metric!

IPnest has also run a 5-year forecast (not yet published) for Design IP, to pass $10B in 2025 and predict a future CAGR (2021 to 2026) of 16.7%. Optimistic? This year-to-year 2022 growth is on-line with this prediction…

Eric Esteve from IPnest

To buy this report, or just discuss about IP, contact Eric Esteve (eric.esteve@ip-nest.com)

Also Read:

Interface IP in 2021: $1.3B, 22% growth and $3B in 2026

Stop-For-Top IP Model to Replace One-Stop-Shop by 2025

Design IP Sales Grew 19.4% in 2021, confirm 2016-2021 CAGR of 9.8%