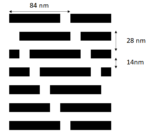

For the 10nm – 5nm nodes, the leading-edge foundries are designing cells which utilize 6 or 7 metal tracks, entailing a wide metal line for every 4 or 5 minimum width lines, respectively (Figure 1).

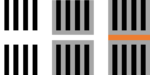

Figure 1. Left: a 7-track cell. Right: a 6-track cell.

This is a fundamental vulnerability for lithography, as defocus can change… Read More