Introduction of 2.5D and 3D multi-die based products are helping extend the boundaries of Moore’s Law, overcoming limitations in speed and capacity for high-end computational tasks. In spite of its critical function within the 3DIC paradigm, the interposer die’s role and related challenges are often neither fully comprehended… Read More

Tag: extraction

Sometimes a Solver is a Suitable Solution

Traditional, rule based, RC extractors rely on a substantial base of assumptions, which are increasingly proving unreliable. Having accurate RC extraction results for parasitic R’s and C’s is extremely important for ensuring proper circuit operation and for optimizing performance and power. Advanced process nodes are making… Read More

Free Webinar: Silvaco 3D Solver Based Extraction for Device and Circuit Designers

Designers spend a lot of time looking at their layouts in 2D. This is done naturally because viewing in 2D is faster and simpler than in 3D. It helps that humans are good at extrapolating from 2D to 3D. Analysis software, such as extraction software also spend a lot of time looking at layouts in 2D. While this is fine for approximate results,… Read More

CEO Interview: Dündar Dumlugöl of Magwel

Magwel CEO Dündar Dumlugöl is well known from his days at Cadence, where I first met him, and for his more recent tenure at Magwel. At Cadence he led the team that first developed Spectre. He has come a long way from the start of his career at IMEC in Belgium. He and I had a chance to have a conversation recently where he offered insights … Read More

Experts Talk at Mentor Booth

It’s less than four weeks to go at DAC 2015 and the program is final now. So I started investigating new technologies, trends, methodologies, and tools that will be unveiled and discussed in this DAC. In the hindsight of the semiconductor industry over the last year, I see 14nm technologies in the realization stage and 10nm beckoning… Read More

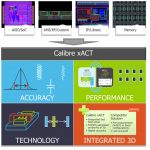

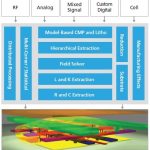

Calibre xACT Shakes Up 16nm and Below Extraction Game

Mentor Graphics made a big announcement regarding SOC extraction at their User2User conference in San Jose during April. Before I get to the meat of the announcement, I’d like to reflect back on the early days of Calibre-DRC at Mentor. I was in Sales at Mentor around 1999, and Calibre-DRC was the new kid on the block. We had to go convince… Read More

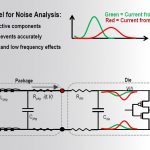

On-Chip Power Integrity Analysis Moves to the Package

Power regimes for contemporary SOC’s now include a large number of voltage domains. Rail voltages are matched closely to the performance and power requirements of various portions of the design. Indeed, some of the supply voltages are so low that the noise margins in these domains is exceedingly low. Higher voltage domains are… Read More

A Deeper Insight into Quantus QRC Extraction Solution

Last month Cadenceannounced its fastest parasitic extraction tool (minimum 5 times better performance compared to other available tools) which can handle growing design sizes with interconnect explosion, number of parasitics and complexities at advanced process nodes including FinFETs, without impacting accuracy of … Read More

Cadence Announces Quantus Next Generation Extraction

Today Cadence announced their next generation extraction solution called Quantus QRC. Actually they are technically announcing it tomorrow, since it is being announced at CDNLive in Korea where it is already Tuesday morning.

As with the other recently announced tools that end in -us, Tempus (timing signoff) and Voltus (power… Read More

EDA for Power Management ICs at DAC

I first met Dundar Dumlugolat Barcelona Design back in 2004, so it was a pleasure to meet with him again at DAClast week and learn more about what his company Magwel has to offer IC designers of power management chips.… Read More