In the lush landscapes of Kumamoto Prefecture, on Japan’s Kyushu Island, TSMC is etching a new chapter in global chip production. The TSMC Kumamoto facility, operationalized through its wholly-owned subsidiary Japan Advanced Semiconductor Manufacturing (JASM), represents the Taiwanese giant’s bold foray into Japan, the first dedicated wafer fab outside Taiwan, the U.S., and Europe.

Announced in 2021, this project embodies a strategic pivot toward diversified, resilient manufacturing. With an initial investment exceeding $8.6 billion, Kumamoto underscores TSMC’s commitment to serving key Asian clients while bolstering Japan’s domestic semiconductor ecosystem.

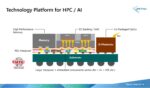

The journey began with groundbreaking in 2022, transforming a sprawling industrial site in Kikuyo Town into a state-of-the-art cleanroom. Construction progressed swiftly, with Taiwanese engineers relocating en masse to oversee integration. By late 2024, JASM’s first fab commenced mass production, focusing on mature yet vital process nodes: 22/28nm and 12/16nm. These nodes are ideal for automotive semiconductors, image sensors, and microcontrollers, sectors where Japanese powerhouses like Sony and Denso dominate.

The facility’s monthly capacity targets 55,000 wafers, powered entirely by renewable energy sources, aligning with Japan’s green manufacturing mandates. As of April 2025, JASM’s workforce has swelled to around 2,400, including 527 new local hires, fostering a blend of Taiwanese expertise and Japanese precision. This infusion has not only created jobs but also sparked a skills renaissance in Kyushu, a region long synonymous with electronics but starved of cutting-edge fabs. This fab was dubbed the “Knight Castle” by locals since construction was done 24 hours a day.

Kumamoto’s strategic imperative is twofold: Geopolitically, it mitigates risks from Taiwan’s exposure to cross-strait tensions, diversifying TSMC’s footprint amid U.S.-China frictions. Economically, it taps into Japan’s resurgence under the “Semiconductor Revival Plan,” backed by subsidies from the Ministry of Economy, Trade and Industry.

This funding is part of a national initiative which aims to reclaim 10% of global chip production by 2030. For TSMC, Kumamoto secures proximity to loyal customers: Sony’s image sensors for smartphones and cameras, Denso’s automotive chips for electric vehicles, and emerging AI peripherals. In an era where automotive semis face slumps, exacerbated by delayed EV adoption, the fab’s specialization offers stability. Industry watchers project profitability by late 2025, with yields already performing robustly.

Yet, expansion hasn’t been seamless. The second fab, earmarked for advanced 6/7nm processes on a 321,000-square-meter plot adjacent to the first, has encountered headwinds. Initially slated for Q1 2025 groundbreaking, construction was deferred to mid-year due to severe traffic congestion from the initial site’s operations (commutes ballooning from 15 minutes to an hour) irking residents. TSMC Chairman C.C. Wei cited these local pains during the June 2025 shareholders’ meeting, emphasizing dialogues with Japanese authorities for infrastructure upgrades. Further delays in 2025 stemmed from softer automotive demand and a pivot toward U.S. investments, pushing mass production to late 2027. TSMC builds fabs closely tied to customer demand so this a good example of intelligent semiconductor business decisions.

Despite these challenges, TSMC reaffirmed its commitment in August 2025 with board member Paul Liu quashing rumors of diminished Japanese focus. The second fab promises elevated capabilities, including 40nm variants for industrial applications, potentially doubling output and attracting more clients.

Beyond wafers, Kumamoto catalyzes regional transformation. Kyushu’s IC production value hit ¥1 trillion in 2024 for the first time in 16 years, fueled by TSMC’s ripple effects. Local suppliers, from equipment makers to materials firms, now furnish 60% of needs, nurturing a self-sustaining cluster. Governor Takashi Kimura has championed community buy-in, securing promises for green spaces and training programs amid wastewater monitoring starting January 2025.

Bottom live: Kumamoto could spawn a third fab post-2030, embedding TSMC deeper in the “semiconductor triangle” of Taiwan, Japan, and the U.S. As AI and EVs propel chip demand, this outpost fortifies supply chains, blending Eastern innovation with Western resilience. In Kumamoto, silicon flows not just as commerce, but as a bridge across borders proving that in the chip wars, collaboration outpaces isolation. For TSMC, it’s a testament to enduring partnerships, for Japan it is a revival etched in silicon, absolutely.

Also Read:

AI-Driven DRC Productivity Optimization: Revolutionizing Semiconductor Design

Exploring TSMC’s OIP Ecosystem Benefits

Breaking the Thermal Wall: TSMC Demonstrates Direct-to-Silicon Liquid Cooling on CoWoS®

TSMC’s Push for Energy-Efficient AI: Innovations in Logic and Packaging