Consolidation continues in the EDA industry with Synopsys announcing today that they acquired Ciranova, a provider of software to automate custom IC layout. Remember that Synopsys invested in Ciranova back in March 2008 and September 2010 (along with Intel Capital, Mentor Graphics and Alloy Ventures), so this deal has some … Read More

MZ Technologies Launches Advanced Packaging Design Video SeriesIn a significant move aimed at empowering semiconductor…Read More

MZ Technologies Launches Advanced Packaging Design Video SeriesIn a significant move aimed at empowering semiconductor…Read More Superhuman AI for Design Verification, Delivered at ScaleThere is a new breed of EDA emerging.…Read More

Superhuman AI for Design Verification, Delivered at ScaleThere is a new breed of EDA emerging.…Read More The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the DefenseIndustrial control systems (ICS) underpin the world’s most…Read More

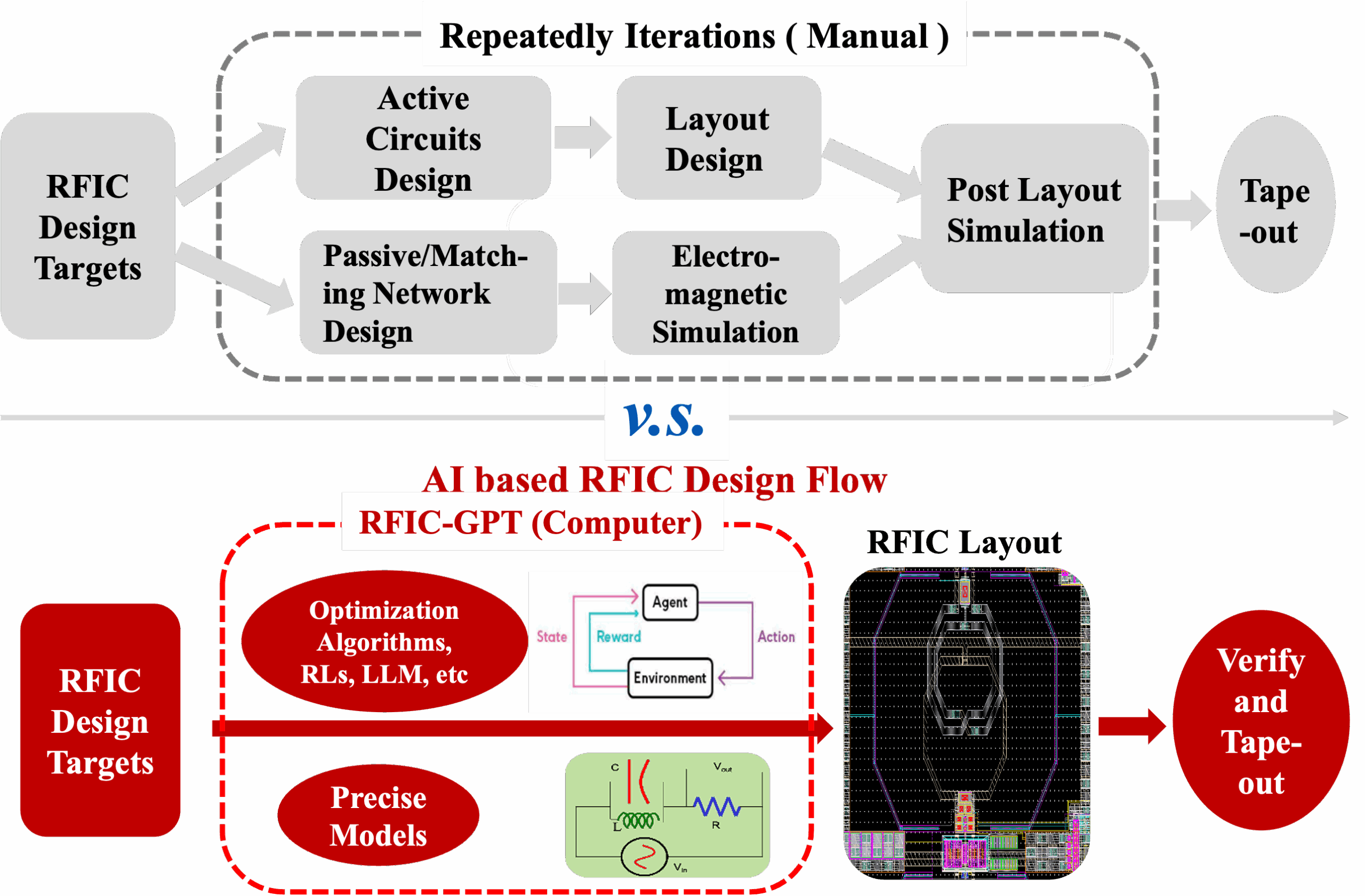

The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the DefenseIndustrial control systems (ICS) underpin the world’s most…Read More Radio Frequency Integrated Circuits (RFICs) Generated by AI Based Design AutomationBy Jason Liu, RFIC-GPT Inc. Radio frequency integrated…Read More

Radio Frequency Integrated Circuits (RFICs) Generated by AI Based Design AutomationBy Jason Liu, RFIC-GPT Inc. Radio frequency integrated…Read MoreThe Coming Battle for AMD’s x86 Hidden Cache

Not yet a year into Rory Read’s term and the AMD board must be considering that the value of the x86 patents and engineering talent is worth much more than the stocks $3B valuation and easier to fathom putting on the auction block than continuing to sell $25 processors into the back channels of China and the Developing World. As I read… Read More

The Unknown in Your Design Can be Dangerous

The SystemVerilog standard defines an X as an “unknown” value which is used to represent when simulation cannot definitely resolve a signal to a “1”, a “0”, or a “Z”. Synthesis, on the other hand, defines an X as a “don’t care”, enabling greater flexibility and optimization. Unfortunately, Verilog RTL simulation semantics often… Read More

Tensilica Joins Wi-Fi Alliance

The Wi-Fi Alliance is an industry consortium dedicated to driving adoption of the various Wi-Fi standards which also go under the rather less catchy name of IEEE 802.11x (where the x varies depending on the generation of the standard, right now a, b, g or n). They also certify devices for interoperability.

Wi-Fi Alliance says that… Read More

SemiWiki.com Analytics Exposed 2012

About 4 years ago some of my semiconductor cohorts urged me to blog. “Hey Dan, you’re a funny guy, write about EDA and IP, make us laugh!” Of course what I think is funny most people think is snarky, which is a nice word for being a smart ass. The traditional semiconductor press was crumbling, the non traditional EDA websites were outdated,… Read More

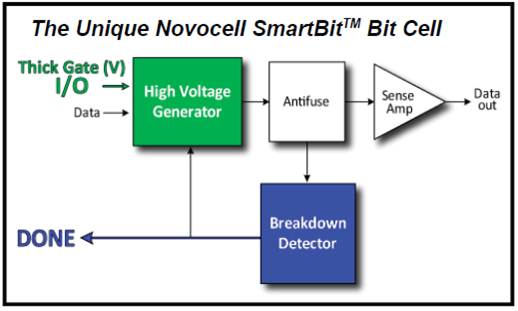

NVM IP: why only anti fuse solution from Novocell Semiconductor is 100% reliable?

The concept of Non Volatile Memory (NVM) block which could be integrated into an ASIC is relatively recent, Novocell for example has been created in 2001. NVM IP integration into an ASIC is a pretty smart technology: integrating from a few bytes to up to Mbits into a SoC can help reducing the number of chips in a system, increase security… Read More

Addressing the Nanometer Digital Design Challenges! (Webinars)

Optimizing logical, physical, electrical, and manufacturing effects, Cadence digital implementation technology eliminates iteration without sacrificing design quality by addressing timing sensitivity, yield variation, and leakage power from the start. … Read More

Synopsys Protocol Analyzer Video

Josefina Hobbs, a solutions architect at Synopsys, demonstrates protocol debug made easy using the Synopsys Protocol Analyzer. This gives users a graphical view of the transfers, transaction, packets and handshaking of a protocol. The video also shows the integration of Synopsys Protocol Analyzer with SpringSoft’s… Read More

Parasitic-Aware Design Flow with Virtuoso

I learn a lot these days through webinars and videos because IC design tools like schematic capture and custom layout are visually oriented. Today I watched a video presentation from Steve Lewis and Stacy Whiteman of Cadence that showed how Virtuoso 6.1.5 is used in a custom IC design flow:… Read More

Addressing the Nanometer Custom IC Design Challenges! (Webinars)

Selectively automating non-critical aspects of custom IC design allows engineers to focus on precision-crafting their designs. Cadence circuit design solutions enable fast and accurate entry of design concepts, which includes managing design intent in a way that flows naturally in the schematic. Using this advanced, parasitic-aware… Read More

Quantum Computing Technologies and Challenges